# SECTION 11 ELECTRICAL AND THERMAL CHARACTERISTICS

#### 11.1 JTAG ELECTRICAL CHARACTERISTICS

The following paragraphs provide information on JTAG electrical and timing specifications. This section is subject to change. For the most recent specifications, contact a Motorola sales office or complete the registration card at the beginning of this manual.

## **JTAG DC Electrical Specifications**

| Characteristic                                                       | Symbol          | Min   | Max   | Unit |

|----------------------------------------------------------------------|-----------------|-------|-------|------|

| Input High Voltage                                                   | VIH             | 2     | Vcc   | ٧    |

| Input Low Voltage                                                    | V <sub>IL</sub> | GND   | 0.8   | >    |

| Undershoot                                                           |                 | _     | 0.8   | >    |

| TCK Input Leakage Current @ 0.5-2.4 V                                | lin             | 20    | 20    | μΑ   |

| TDO Hi-Z (Off-State) Leakage Current @ 0.5-2.4 V                     | ITST            | 20    | 20    | μА   |

| Signal Low Input Current, V <sub>IL</sub> = 0.8 V<br>TMS, TDI, TRST  | IL.             | -1.1  | -0.18 | mA   |

| Signal High Input Current, V <sub>IH</sub> = 2.0 V<br>TMS, TDI, TRST | Чн              | -0.94 | -0.16 | mA   |

| TDO Output High Voltage                                              | Voн             | 2.4   | _     | ٧    |

| TDO Output Low Voltage                                               | VOL             | _     | 0.5   | ٧    |

| Capacitance*, V <sub>in</sub> = 0 V, f = 1 MHz                       | Cin             | _     | 25    | pF   |

<sup>\*</sup>Capacitance is periodically sampled rather than 100% tested.

MOTOROLA M68040 USER'S MANUAL 11-1

## JTAG Timing Specifications (All Operating Frequencies)

| Num | Characteristic                          | Min | Max | Unit |

|-----|-----------------------------------------|-----|-----|------|

|     | TCK Frequency of Operation              | 0   | 10  | MHz  |

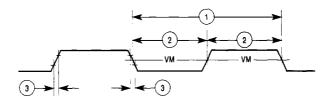

| 1   | TCK Cycle Time                          | 100 | _   | ns   |

| 2   | TCK Clock Pulse Width Measured at 1.5 V | 40  |     | ns   |

| 3   | TCK Rise and Fall Times                 | 0   | 10  | ns   |

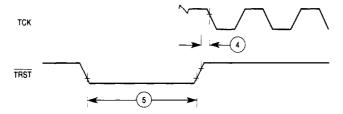

| 4   | TRST Setup Time to TCK Falling Edge     | 40  | _   | ns   |

| 5   | TRST Assert Time                        | 100 | _   | ns   |

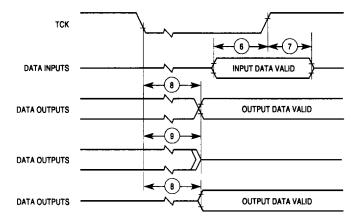

| 6   | Boundary Scan Input Data Setup Time     | 50  | _   | ns   |

| 7   | Boundary Scan Input Data Hold Time      | 50  | _   | ns   |

| 8   | TCK to Output Data Valid                | 0   | 50  | ns   |

| 9   | TCK to Output High Impedance            | 0   | 50  | ns   |

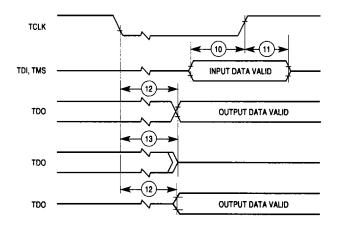

| 10  | TMS, TDI Data Setup Time                | 20  | _   | ns   |

| 11  | TMS, TDI Data Hold Time                 | 5_  |     | ns   |

| 12  | TCK to TDO Data Valid                   | 0   | 20  | ns   |

| 13  | TCK to TDO High Impedance               | 0   | 20  | ns   |

Figure 11-1. Clock Input Timing Diagram

Figure 11-2. TRST Timing Diagram

Figure 11-3. Boundary Scan Timing Diagram

Figure 11-4. Test Access Port Timing Diagram

## 11.2 MC68040 ELECTRICAL CHARACTERISTICS

The following paragraphs provide information on the maximum rating and thermal characteristics for the MC68040. This section is subject to change. For the most recent specifications, contact a Motorola sales office or complete the registration card at the beginning of this manual.

## MC68040 Maximum Ratings

| Characteristic                         | Symbol           | Value        | Unit |

|----------------------------------------|------------------|--------------|------|

| Supply Voltage                         | Vcc              | -0.3 to +7.0 | ٧    |

| Input Voltage                          | V <sub>in</sub>  | -0.5 to +7.0 | ٧    |

| Maximum Operating Junction Temperature | Tj               | 110          | °C   |

| Minimum Operating Ambient Temperature  | TA               | 0            | °C   |

| Storage Temperature Range              | T <sub>stg</sub> | -55 to 150   | °C   |

## MC68040 Thermal Characteristics—PGA Package

| Characteristic                       | Symbol | Value | Rating |

|--------------------------------------|--------|-------|--------|

| Thermal Resistance, Junction to Case | θJC    | 3     | °C/W   |

## MC68040 DC Electrical Specifications (V<sub>CC</sub> = 5.0 Vdc ±5 %)

| Characteristic                                                                                                                       | Symbol          | Min  | Max   | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-------|------|

| Input High Voltage                                                                                                                   | VIH             | 2    | Vcc   | ٧    |

| Input Low Voltage                                                                                                                    | ViL             | GND  | 0.8   | >    |

| Undershoot                                                                                                                           | _               | _    | 0.8   | ٧    |

| Input Leakage Current @ 0.5/2.4 V  AVEC, BCLK, BG, CDIS, MDIS, IPLX, PCLK, RSTI, SCx, TBI, TLNx, TCI, TCK, TEA                       | l <sub>in</sub> | 20   | 20    | μΑ   |

| Hi-Z (Off-State) Leakage Current @ 0.5/2.4 V<br>An, BB, CIOUT, Dn, LOCK, LOCKE, R/W, SIZx, TA, TDO,<br>TIP, TMx, TLNx, TS, TTx, UPAx | ITSI            | 20   | 20    | μΑ   |

| Signal Low Input Current, VIL = 0.8 V<br>TMS, TDI, TRST                                                                              | IIL             | -1.1 | -0.18 | mA   |

| Signal High Input Current, V <sub>IH</sub> = 2.0 V<br>TMS, TDI, TRST                                                                 | lн              | 0.94 | -0.16 | mA   |

| Output High Voltage, IOH = 5 mA (Small Buffer Mode)                                                                                  | VOH             | 2.4  |       | ٧    |

| Output Low Voltage, IOL = 5 mA (Small Buffer Mode)                                                                                   | VOL             |      | 0.5   | ٧    |

| Output High Voltage, I <sub>OH</sub> = 55 mA (Large Buffer Mode)                                                                     | Voн             | 2.4  | -     | V    |

| Output Low Voltage, IOL = 55 mA (Large Buffer Mode)                                                                                  | VOL             | _    | 0.5   | ٧    |

| Capacitance*, Vin = 0 V, f = 1 MHz                                                                                                   | Cin             |      | 25    | ρF   |

<sup>\*</sup>Capacitance is periodically sampled rather than 100% tested.

## MC68040 Power Dissipation

| Buffer Mode                                                  | 25 MHz                         | 33 MHz | 40 MHz<br>(Preliminary) |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------|--------------------------------|--------|-------------------------|--|--|--|--|--|--|--|--|

| Worst Case (V <sub>CC</sub> = 5.25 V , T <sub>A</sub> = 0°C) |                                |        |                         |  |  |  |  |  |  |  |  |

| Small Unterminated, IOL = IOH = 5 mA                         | 6.3 W                          | 7.7 W  | 8.4 W                   |  |  |  |  |  |  |  |  |

| Large Unterminated, IOL = IOH = 5 mA                         | 6.6 W                          | 8.0 W  | 8.7 W                   |  |  |  |  |  |  |  |  |

| Large Terminated, 50 Ω, 2.5 V, IOL = IOH = 55 mA             | 8.0 W                          | 9.5 W  | 10.2 W                  |  |  |  |  |  |  |  |  |

| Typical Values (V <sub>C</sub>                               | C = 5 V, T <sub>J</sub> = 90°0 | C)*    |                         |  |  |  |  |  |  |  |  |

| Small                                                        | 4.3 W                          | 5.4 W  | 5.9 W                   |  |  |  |  |  |  |  |  |

| Large Unterminated                                           | 4.6 W                          | 5.7 W  | 6.2 W                   |  |  |  |  |  |  |  |  |

| Large Terminated, 50 Ω, 2.5 V                                | 5.8 W                          | 6.9 W  | 7.4 W                   |  |  |  |  |  |  |  |  |

<sup>\*</sup>This information is for system reliability purposes.

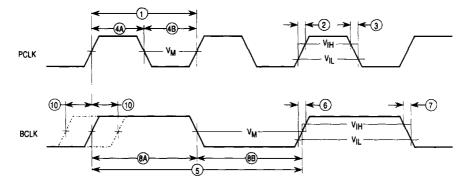

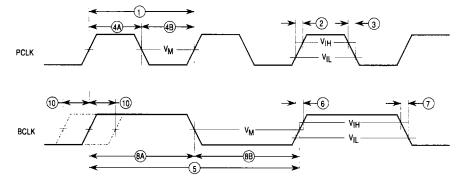

## MC68040 Clock AC Timing Specifications (see Figure 11-5)

These specifications are for 25, 33, and 40 MHz; the 40 MHz specifications are preliminary.

|     |                                         | 25 MHz |       | 33 1  | ИНz   |       | MHz<br>ninary) |      |

|-----|-----------------------------------------|--------|-------|-------|-------|-------|----------------|------|

| Num | Characteristic                          | Min    | Max   | Min   | Max   | Min   | Max            | Unit |

|     | Frequency of Operation                  | 16.67  | 25    | 16.67 | 33    | 20    | 40             | MHz  |

| 1   | PCLK Cycle Time                         | 20     | 30    | 15    | 30    | 12.5  | 25             | ns   |

| 2   | PCLK Rise Time                          |        | 1.7   | 1     | 1.7   |       | 1.5            | ns   |

| 3   | PCLK Fall Time                          | _      | 1.6   | 1     | 1.6   | -     | 1.5            | ns   |

| 4   | PCLK Duty Cycle Measured at 1.5 V       | 47.50  | 52.50 | 46.67 | 53.33 | 46.00 | 54.00          | %    |

| 4a* | PCLK Pulse Width High Measured at 1.5 V | 9.50   | 10.50 | 7     | 8     | 5.75  | 6.75           | ns   |

| 4b* | PCLK Pulse Width Low Measured at 1.5 V  | 9.50   | 10.50 | 7     | 8     | 5.75  | 6.75           | ns   |

| 5   | BCLK Cycle Time                         | 40     | 60    | 30    | 60    | 25    | 50             | ns   |

| 6,7 | BCLK Rise and Fall Time                 | -      | 4     |       | 3     |       | 3              | ns   |

| 8   | BCLK Duty Cycle Measured at 1.5 V       | 40     | 60    | 40    | 60    | 40    | 60             | %    |

| 8a* | BCLK Pulse Width High Measured at 1.5 V | 16     | 24    | 12    | 18    | 10    | 15             | ns   |

| 8b* | BCLK Pulse Width Low Measured at 1.5 V  | 16     | 24    | 12    | 18    | 10    | 15             | ns   |

| 9   | PCLK, BCLK Frequency Stability          |        | 1000  |       | 1000  |       | 1000           | ppm  |

| 10  | PCLK to BCLK Skew                       |        | 9     |       | n/a   | 1     | n/a            | ns   |

<sup>\*</sup>Specification value at maximum frequency of operation.

Figure 11-5. Clock Input Timing Diagram

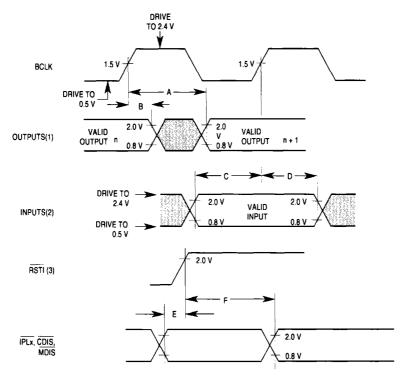

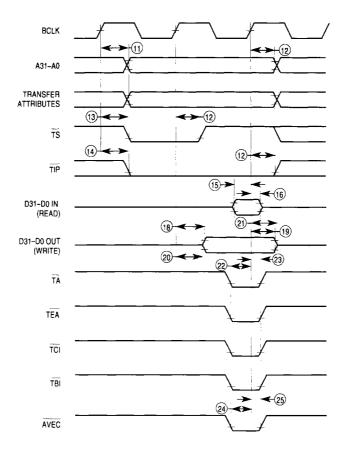

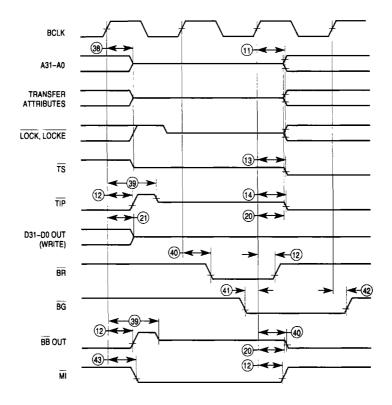

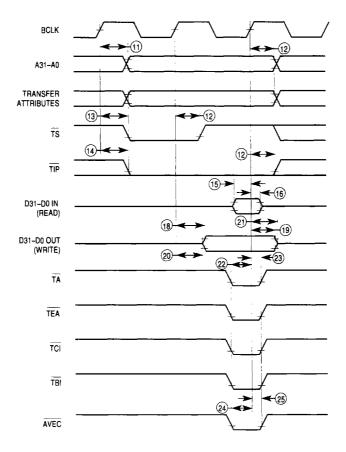

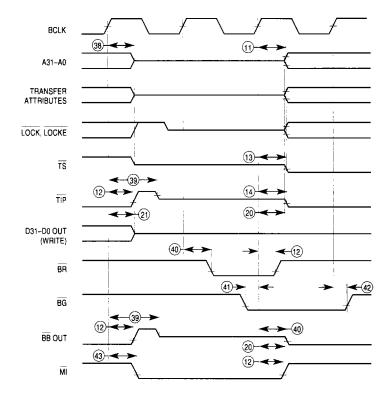

#### MC68040 Output AC Timing Specifications (See Figures 11-6-11-11)

These specifications are for 25, 33, and 40 MHz; the 40 MHz specifications are preliminary.

|                     |                                                                                               | 25 MHz |                 |     | 33 MHz           |      |                                       | 40 Mhz<br>(Preliminary) |                  |                    |     |                                      |     |      |

|---------------------|-----------------------------------------------------------------------------------------------|--------|-----------------|-----|------------------|------|---------------------------------------|-------------------------|------------------|--------------------|-----|--------------------------------------|-----|------|

|                     |                                                                                               | Lar    | ge <sup>1</sup> | Sm  | all <sup>2</sup> | Lar  | Large <sup>1</sup> Small <sup>2</sup> |                         | all <sup>2</sup> | Large <sup>1</sup> |     | arge <sup>1</sup> Small <sup>2</sup> |     |      |

| Num                 | Characteristic                                                                                | Min    | Max             | Min | Max              | Min  | Max                                   | Min                     | Max              | Min                | Max | Min                                  | Max | Unit |

| 113                 | BCLK to Address CIOUT, LOCK,<br>LOCKE, R/W, SIZx, TLN, TMx, TTx,<br>UPAx Valid                | 9      | 21              | 9   | 30               | 6.50 | 18                                    | 6.50                    | 25               | 5.25               | 16  | 5.25                                 | 24  | ns   |

| 12                  | BCLK to Output Invalid<br>(Output Hold)                                                       | 9      |                 | 9   | 1                | 6.50 | 1                                     | 6.50                    | 1                | 5.25               | 1   | 5.25                                 | 1   | ns   |

| 13                  | BCLK to TS Valid                                                                              | 9      | 21              | 9   | 30               | 6.50 | 18                                    | 6.50                    | 25               | 5.25               | 16  | 5.25                                 | 24  | ns   |

| 14                  | BCLK to TIP Valid                                                                             | 9      | 21              | 9   | 30               | 6.50 | 18                                    | 6.50                    | 25               | 5.25               | 17  | 5.25                                 | 24  | ns   |

| 18 <sup>4</sup>     | BCLK to Data Out Valid                                                                        | 9      | 23              | 9   | 32               | 6.50 | 20                                    | 6.50                    | 27               | 5.25               | 18  | 5.25                                 | 26  | ns   |

| 194                 | BCLK to Data Out Invalid (Output Hold)                                                        | 9      | 1               | 9   | 1                | 6.50 | 1                                     | 6.50                    |                  | 5.25               | _   | 5.25                                 | 1   | ns   |

| 20 <sup>3,4</sup>   | BCLK to Output Low Impedance                                                                  | 9      | -               | 9   | ı                | 6.50 |                                       | 6.50                    | -                | 5.25               |     | 5.25                                 | _   | ns   |

| 21 <sup>5</sup>     | BCLK to Data-Out High Impedance                                                               | 9      | 20              | 9   | 20               | 6.50 | 17                                    | 6.50                    | 17               | 5.25               | 16  | 5.25                                 | 16  | ns   |

| 26 <sup>3</sup>     | BCLK to Multiplexed<br>Address Valid                                                          | 19     | 31              | 19  | 40               | 14   | 26                                    | 14                      | 33               | 13                 | 25  | 13                                   | 32  | ns   |

| 273,5               | BCLK to Multiplexed<br>Address Driven                                                         | 19     | _               | 19  | _                | 14   |                                       | 14                      |                  | 13                 | _   | 13                                   |     | ns   |

| 28 <sup>3,4,5</sup> | BCLK to Multiplexed Address<br>High Impedance                                                 | 9      | 18              | 9   | 18               | 6.50 | 15                                    | 6.50                    | 15               | 5.25               | 14  | 5.25                                 | 14  | ns   |

| 294,5               | BCLK to Multiplexed<br>Data Driven                                                            | 19     |                 | 19  | _                | 14   | 20                                    | 14                      | 20               | 13                 | 19  | 13                                   | 19  | ns   |

| 30 <sup>4</sup>     | BCLK to Multiplexed Data Valid                                                                | 19     | 33              | 19  | 42               | 14   | 28                                    | 14                      | 35               | 13                 | 27  | 13                                   | 34  | ns   |

| 383                 | BCLK to Address, CIOUT, LOCK,<br>LOCKE, R/W, SIZx, TS, TLNx, TMx,<br>TTx, UPAx High Impedance | 9      | 18              | 9   | 18               | 6.50 | 15                                    | 6.50                    | 15               | 5.25               | 14  | 5.25                                 | 14  | ns   |

| 39                  | BCLK to BB, TA, TIP<br>High Impedance                                                         | 19     | 28              | 19  | 28               | 14   | 23                                    | 14                      | 23               | 11.5               | 22  | 11.5                                 | 22  | ns   |

| 40                  | BCLK to BR, BB Valid                                                                          | 9      | 21              | 9   | 30               | 6.50 | 18                                    | 6.50                    | 25               | 5.25               | 16  | 5.25                                 | 24  | ns   |

| 43                  | BCLK to MI Valid                                                                              | 9      | 21              | 9   | 30               | 6.50 | 18                                    | 6.50                    | 25               | 5.25               | 17  | 5.25                                 | 24  | ns   |

| 48                  | BCLK to TA Valid                                                                              | 9      | 21              | 9   | 30               | 6.50 | 18                                    | 6.50                    | 25               | 5.25               | 17  | 5.25                                 | 24  | ns   |

| 50                  | BCLK to IPEND, PSTx, RSTO Valid                                                               | 9      | 21              | 9   | 30               | 6.50 | 18                                    | 6.50                    | 25               | 5.25               | 17  | 5.25                                 | 24  | ns   |

#### NOTES:

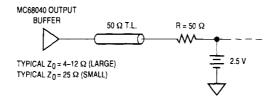

- Output timing is specified for a valid signal measured at the pin. Large buffer timing is specified driving a 50 Ω transmission line with a length characterized by a 2.5-ns one-way propagation delay, terminated through 50 Ω to 2.5 V. Large buffer output impedance is 4–12 Ω, resulting in incident wave switching for this environment. All large buffer outputs must be terminated to guarantee operation.

- Small buffer timing is specified driving an unterminated 30 Ω transmission line with a length characterized by a 2.5 ns one-way propagation delay. Small buffer output impedance is typically 30 Ω; the small buffer specifications include approximately 5 ns for the signal to propagate the length of the transmission line and back.

- Timing specifications 11, 20, and 38 for address bus output timing apply when normal bus operation is selected.

Specifications 26, 27, and 28 should be used when the multiplexed bus mode of operation is enabled.

- Timing specifications 18 and 19 for data bus output timing apply when normal bus operation is selected.

Specifications 28 and 29 should be used when the multiplexed bus mode of operation is enabled.

- 5. Timing specifications 21, 27, 28, and 29 are measured from BCLK edges. By design, the MC68040 cannot drive address and data simultaneously during multiplexed operations.

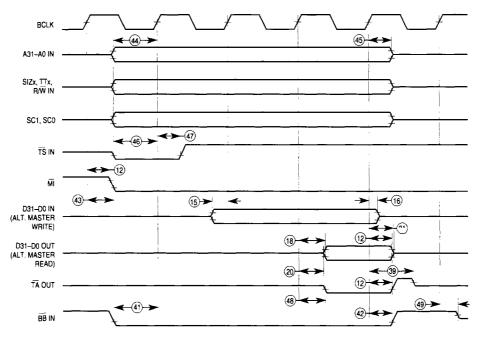

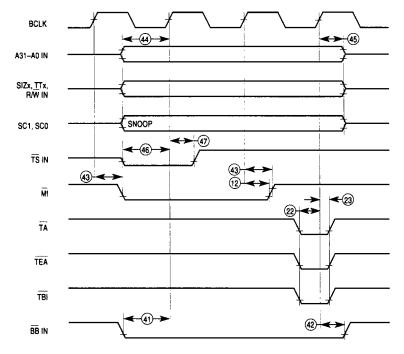

# MC68040 Input AC Timing Specifications (see Figures 11-8–11-11) These specifications are for 25, 33, and 40 MHz; the 40 MHz specifications are preliminary.

|     |                                                               | 25  | ИНZ | 33 1 | MHz  |      | MHz<br>ninary) |      |

|-----|---------------------------------------------------------------|-----|-----|------|------|------|----------------|------|

| Num | Characteristic                                                | Min | Max | Min  | Max  | Min. | Max.           | Unit |

| 15  | Data-In Valid to BCLK (Setup)                                 | 5   | _   | 4    | _    | 3    |                | ns   |

| 16  | BCLK to Data-In Invalid (Hold)                                | 4   | 1   | 4    |      | 3    | _              | ns   |

| 17  | BCLK to Data-In High Impedance<br>(Read Followed by Write)    | _   | 49  | 1    | 36.5 | _    | 30.25          | ns   |

| 22a | TA Valid to BCLK (Setup)                                      | 10  |     | 10   |      | 8    | -              | ns   |

| 22b | TEA Valid to BCLK (Setup)                                     | 10  | -   | 10   |      | 9    | -              | ns   |

| 22c | TCl Valid to BCLK (Setup)                                     | 10  | _   | 10   | -    | 9    | Ì              | ns   |

| 22d | TBI Valid to BCLK (Setup)                                     | 11  |     | 10   |      | 9    | 1              | ns   |

| 23  | BCLK to TA, TEA, TCI, TBI Invalid (Hold)                      | 2   |     | 2    |      | 2    |                | ns   |

| 24  | AVEC Valid to BCLK (Setup)                                    | 5   | -   | 5    | _    | 5    | 1              | ns   |

| 25  | BCLK to AVEC Invalid (Hold)                                   | 2   | _   | 2    | _    | 2    |                | ns   |

| 31  | DLE Width High                                                | 8   | _   | 8    | _    | 8    |                | ns   |

| 32  | Data-In Valid to DLE (Setup)                                  | 2   | _   | 2    | _    | 2    |                | ns   |

| 33  | DLE to Data-In Invalid (Hold)                                 | 8   |     | 8    | _    | 8    | 1              | ns   |

| 34  | BCLK to DLE Hold                                              | 3   |     | 3    | _    | 3    | -              | ns   |

| 35  | DLE High to BCLK                                              | 16  | _   | 12   | _    | 12   | _              | ns   |

| 36  | Data-In Valid to BCLK (DLE Mode Setup)                        | 5   |     | 5    |      | 5    |                | ns   |

| 37  | BCLK to Data-In Invalid (DLE Mode Hold)                       | 4   |     | 4    |      | 4    | _              | ns   |

| 41a | BB Valid to BCLK (Setup)                                      | 7   |     | 7    | _    | 7    | _              | ns   |

| 41b | BG Valid to BCLK (Setup)                                      | 8   |     | 7    | _    | 7    | _              | ns   |

| 41c | CDIS, MDIS Valid to BCLK (Setup)                              | 10  | _   | 8    |      | 8    |                | ns   |

| 41d | IPLx Valid to BCLK (Setup)                                    | 4   |     | 3    | _    | 3    | _              | ns   |

| 42  | BCLK to BB, BG, CDIS, IPLx, MDIS Invalid (Hold)               | 2   | _   | 2    | _    | 2    | _              | ns   |

| 44a | Address Valid to BCLK (Setup)                                 | 8   | _   | 7    | _    | 7    |                | ns   |

| 44b | SIZx Valid to BCLK (Setup)                                    | 12  | _   | 8    | _    | 8    | _              | ns   |

| 44c | TTx Valid to BCLK (Setup)                                     | 6   | _   | 8.5  |      | 8.5  | _              | ns   |

| 44d | R/W Valid to BCLK (Setup)                                     | 6   | _   | 5    | _    | 5    |                | ns   |

| 44e | SCx Valid to BCLK (Setup)                                     | 10  |     | 11   | _    | 8    | -              | ns   |

| 45  | BCLK to Address,SIZx, TTx, R/W, SCx Invalid (Hold)            | 2   |     | 2    |      | 2    |                | ns   |

| 46  | TS Valid to BCLK (Setup)                                      | 5   | _   | 9    | _    | 7    |                | ns   |

| 47  | BCLK to TS Invalid (Hold)                                     | 2   |     | 2    | _    | 2    |                | ns   |

| 49  | BCLK to BB High Impedance<br>(MC68040 Assumes Bus Mastership) |     | 9   | _    | 9    | _    | 9              | ns   |

| 51  | RSTI Valid to BCLK                                            | 5   | _   | 4    | _    | 4    | _              | ns   |

| 52  | BCLK to ASTI Invalid                                          | 2   | -   | 2    |      | 2    | _              | ns   |

| 53  | Mode Select Setup to RSTI Negated                             | 20  | _   | 20   |      | 20   | _              | ns   |

| 54  | RSTI Negated to Mode Selects Invalid                          | 2   | _   | 2    | _    | 2    |                | ns   |

#### NOTES

- 1. This output timing is applicable to all parameters specified relative to the rising edge of the clock.

- 2. This input timing is applicable to all parameters specified relative to the rising edge of the clock.

- 3. This timing is applicable to all parameters specified relative to the negation of the RSTI signal.

#### LEGEND:

- A. Maximum output delay specification.

- B. Minimum output hold time.

- C. Minimum input setup time specification.

- D. Minimum input hold time specification.

- E. Mode select setup time to RSTI negated.

- F. Mode select hold time from RSTI negated.

Figure 11-6. Drive Levels and Test Points for AC Specifications

NOTE: Transfer Attribute Signals = UPAx, SIZx, TTx, TMx, TLNx,  $R_i\overline{W}$ ,  $\overline{LOCK}$ ,  $\overline{LOCK$

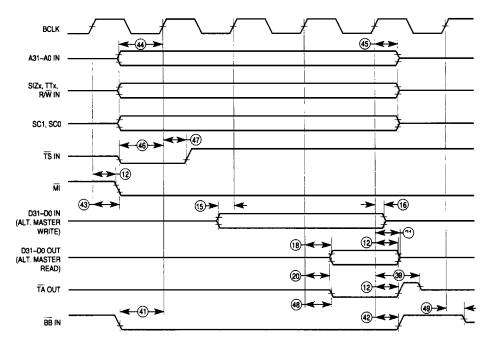

Figure 11-7. Read/Write Timing

NOTE: Transfer Attribute Signals = UPAx, SIZx, TTx, TMx, TLNx, R/W, CIOUT

Figure 11-8. Bus Arbitration Timing

Figure 11-9. Snoop Hit Timing

**MOTOROLA**

Figure 11-10. Snoop Miss Timing

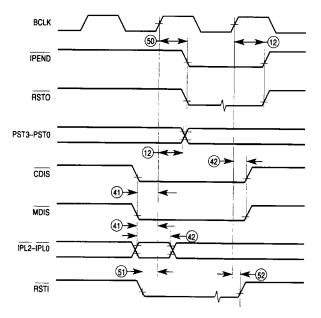

Figure 11-11. Other Signal Timing

### 11.3 MC68LC040 ELECTRICAL CHARACTERISTICS

The following paragraphs provide information on the maximum rating and thermal characteristics for the MC68LC040. This section is subject to change. For the most recent specifications, contact a Motorola sales office or complete the registration card at the beginning of this manual.

### MC68LC040 Maximum Ratings

| Characteristic                         | Symbol           | Value        | Unit |

|----------------------------------------|------------------|--------------|------|

| Supply Voltage                         | Vcc              | -0.3 to +7.0 | ٧    |

| Input Voltage                          | V <sub>in</sub>  | -0.5 to +7.0 | V    |

| Maximum Operating Junction Temperature | TJ               | 110          | °C   |

| Minimum Operating Ambient Temperature  | TA               | 0            | °C   |

| Storage Temperature Range              | T <sub>stg</sub> | -55 to 150   | °C   |

## MC68LC040 Thermal Characteristics PGA Package

| Characteristic                       | Symbol | Value | Rating |

|--------------------------------------|--------|-------|--------|

| Thermal Resistance, Junction to Case | θЈС    | 3     | °C/W   |

## MC68LC040 DC Electrical Specifications (V<sub>CC</sub> = 5.0 Vdc ±5 %)

| Characteristic                                                                                                                       | Symbol           | Min   | Max   | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|-------|------|

| Input High Voltage                                                                                                                   | VIH              | 2     | Vcc   | V    |

| Input Low Voltage                                                                                                                    | VIL              | GND   | 0.8   | V    |

| Undershoot                                                                                                                           |                  | _     | 0.8   | V    |

| Input Leakage Current @ 0.5–2.4 V<br>AVEC, BCLK, BG, CDIS, MDIS, IPLx, PCLK, RSTI, SCx,<br>TBI, TLNx, TCI, TCK, TEA                  | † <sub>in</sub>  | 20    | 20    | μΑ   |

| Hi-Z (Off-State) Leakage Current @ 0.5-2.4 V<br>An, BB, CIOUT, Dn, LOCK, LOCKE, R/W, SIZx, TA, TDO,<br>TIP, TMx, TLNx, TS, TTx, UPAx | <sup>‡</sup> TSI | 20    | 20    | μΑ   |

| Signal Low Input Current, V <sub>IL</sub> = 0.8 V<br>TMS, TDI, TRST                                                                  | IJL              | -1.1  | -0.18 | mA   |

| Signal High Input Current, V <sub>IH</sub> = 2.0 V<br>TMS, TDI, TRST                                                                 | IIH              | -0.94 | -0.16 | mA   |

| Output High Voltage, IOH = 5 mA                                                                                                      | ∨он              | 2.4   | _     | V    |

| Output Low Voltage, IOL = 5 mA                                                                                                       | VOL              | _     | 0.5   | V    |

| Capacitance*, V <sub>in =</sub> 0 V, f = 1 MHz                                                                                       | C <sub>in</sub>  |       | 25    | pF   |

<sup>\*</sup>Capacitance is periodically sampled rather than 100% tested.

# MC68LC040 Power Dissipation

| Frequency                      | Watts                  |

|--------------------------------|------------------------|

| Maximum Values (Vo             | CC = 5.25 V, TA = 0°C) |

| 20 MHz                         | 4.0                    |

| 25 MHz                         | 5.0                    |

| 33 MHz                         | 6.3                    |

| Typical Values (V <sub>C</sub> | C = 5 V, TA = 25°C)*   |

| 20 MHz                         | 3.0                    |

| 25 MHz                         | 3.8                    |

| 33 MHz                         | 4.8                    |

<sup>\*</sup>This information is for system reliability purposes.

## MC68LC040 Clock AC Timing Specifications (see Figure 11-12)

|     |                                         | 20 1  | MHz  | 25 MHz |      | 33 MHz |       |      |

|-----|-----------------------------------------|-------|------|--------|------|--------|-------|------|

| Num | Characteristic                          | Min   | Max  | Min    | Max  | Min    | Max   | Unit |

|     | Frequency of Operation                  | 16.67 | 20   | 16.67  | 25   | 16.67  | 33    | MHz  |

| 1   | PCLK Cycle Time                         | 25    | 30   | 20     | 30   | 15     | 30    | ns   |

| 2   | PCLK Rise Time                          |       | 1.7  |        | 1.7  | _      | 1.7   | ns   |

| 3   | PCLK Fall Time                          |       | 1.6  | _      | 1.6  |        | 1.6   | ns   |

| 4   | PCLK Duty Cycle Measured at 1.5 V       | 48    | 52   | 47.5   | 52.5 | 46.67  | 53.33 | %    |

| 4a* | PCLK Pulse Width High Measured at 1.5 V | 12    | 13   | 9.5    | 10.5 | 7      | 8     | ns   |

| 4b* | PCLK Pulse Width Low Measured at 1.5 V  | 12    | 13   | 9.5    | 10.5 | 7      | 8     | ns   |

| 5   | BCLK Cycle Time                         | 50    | 60   | 40     | 60   | 30     | 60    | ns   |

| 6,7 | BCLK Rise and Fall Time                 |       | 4    |        | 4    |        | 3     | ns   |

| 8   | BCLK Duty Cycle Measured at 1.5 V       | 40    | 60   | 40     | 60   | 40     | 60    | %    |

| 8a* | BCLK Pulse Width High Measured at 1.5 V | 20    | 30   | 16     | 24   | 12     | 18    | ns   |

| 8b* | BCLK Pulse Width Low Measured at 1.5 V  | 20    | 30   | 16     | 24   | 12     | 18    | ns   |

| 9   | PCLK, BCLK Frequency Stability          | _     | 1000 | _      | 1000 | _      | 1000  | ppm  |

| 10  | PCLK to BCLK Skew                       |       | 9    |        | 9    | _      | n/a   | ns   |

<sup>\*</sup>Specification value at maximum frequency of operation.

MC680LC40 Output AC Timing Specifications (see Figures 11-13\*-11-17)

|     |                                                                                               | 20 1 | MHz | 25 N | ИНZ | 33 MHz |     |      |

|-----|-----------------------------------------------------------------------------------------------|------|-----|------|-----|--------|-----|------|

| Num | Characteristic                                                                                | Min  | Max | Min  | Max | Min    | Max | Unit |

| 11  | 11 BCLK to Address, CIOUT, LOCK, LOCKE, PSTx, R/W, SIZx, TLNx,TMx, TTx, UPAx Valid            |      | 35  | 9    | 30  | 6.5    | 25  | ns   |

| 12  | BCLK to Output Invalid (Output Hold)                                                          | 11.5 | 1   | 9    | -   | 6.5    |     | ns   |

| 13  | BCLK to TS Valid                                                                              | 11.5 | 35  | 9    | 30  | 6.5    | 25  | ns   |

| 14  | BCLK to TIP Valid                                                                             | 11.5 | 35  | 9    | 30  | 6.5    | 25  | ns   |

| 18  | BCLK to Data-Out Valid                                                                        | 11.5 | 37  | 9    | 32  | 6.5    | 27  | ns   |

| 19  | BCLK to Data-Out Invalid (Output Hold)                                                        | 11.5 | _   | 9    |     | 6.5    | _   | ns   |

| 20  | BCLK to Output Low Impedance                                                                  | 11.5 | _   | 9    |     | 6.5    | _   | ns   |

| 21  | BCLK to Data-Out High Impedance                                                               | 11.5 | 25  | 9    | 20  | 6.5    | 17  | ns   |

| 38  | BCLK to Address, CIOUT, LOCK, LOCKE,<br>R/W, SIZx, TS, TLNx, TMx, TTx, UPAx High<br>Impedance | 11.5 | 23  | 9    | 18  | 6.5    | 15  | ns   |

| 39  | BCLK to BB, TA, TIP High Impedance                                                            | 23   | 33  | 19   | 28  | 14     | 25  | ns   |

| 40  | BCLK to BR, BB Valid                                                                          | 11.5 | 35  | 9    | 30  | 6.5    | 23  | ns   |

| 43  | BCLK to MI Valid                                                                              | 11.5 | 35  | 9    | 30  | 6.5    | 25  | ns   |

| 48  | BCLK to TA Valid                                                                              | 11.5 | 35  | 9    | 30  | 6.5    | 25  | ns   |

| 50  | BCLK to IPEND, PSTx, RSTO Valid                                                               | 11.5 | 35  | 9    | 30  | 6.5    | 25  | ns   |

<sup>\*</sup>Output timing is specified for a valid signal measured at the pin. Timing is specified driving an unterminated  $30-\Omega$  transmission line with a length characterized by a 2.5-ns one-way propagation delay. Buffer output impedance is typically  $30~\Omega$ ; the buffer specifications include approximately 5 ns for the signal to propagate the length of the transmission line and back.

MOTOROLA M68040 USER'S MANUAL 11-17

## MC680LC40 Input AC Timing Specifications (See Figures 11-14-11-17)

|     |                                                                 | 20 1   | MHz    | 25  | MHz     | 33 1 | ИНZ           |      |

|-----|-----------------------------------------------------------------|--------|--------|-----|---------|------|---------------|------|

| Num | Characteristic                                                  | Min    | Max    | Min | Max     | Min  | Max           | Unit |

| 15  | Data-In Valid to BCLK (Setup)                                   | 6      |        | 5   | _       | 4    | _             | ns   |

| 16  | BCLK to Data-In Invalid (Hold)                                  | 5      | _      | 4   | _       | 4    | _             | ns   |

| 17  | BCLK to Data-In High Impedance<br>(Read Followed by Write)      | _      | 61     |     | 49      | _    | 36.5          | ns   |

| 22a | TA Valid to BCLK (Setup)                                        | 12.5   |        | 10  | -       | 10   | _             | ns   |

| 22b | TEA Valid to BCLK (Setup)                                       | 12.5   |        | 10  | _       | 10   | _             | ns   |

| 22c | TCI Valid to BCLK (Setup)                                       | 12.5   |        | 10  | _       | 10   | _             | ns   |

| 22d | TBI Valid to BCLK (Setup)                                       | 14     | _      | 11  | _       | 10   | _             | ns   |

| 23  | BCLK to TA, TEA, TCI, TBI Invalid (Hold)                        | 2.5    |        | 2   | -       | 2    | _             | ns   |

| 24  | AVEC Valid to BCLK (Setup)                                      | 6      | _      | 5   | _       | 5    | _             | ns   |

| 25  | BCLK to AVEC Invalid (Hold)                                     | 2.5    |        | 2   | _       | 2    | _             | ns   |

| 41a | BB Valid to BCLK (Setup)                                        | 8      | _      | 7   |         | 7    | _             | ns   |

| 41b | BG Valid to BCLK (Setup)                                        | 10     | _      | 8   | _       | 7    | _             | ns   |

| 41c | CDIS, MDIS Valid to BCLK (Setup)                                | 12.5   |        | 10  |         | 8    | _             | ns   |

| 41d | IPLx Valid to BCLK (Setup)                                      | 5      | _      | 4   | ****    | 3    | _             | ns   |

| 42  | BCLK to BB, BG, CDIS, MDIS, IPLx Invalid (Hold)                 | 2.5    | ****** | 2   | _       | 2    | _             | ns   |

| 44a | Address Valid to BCLK (Setup)                                   | 10     | _      | 8   |         | 7    | _             | ns   |

| 44b | SIZx Valid to BCLK (Setup)                                      | 15     | _      | 12  | _       | 8    | _             | ns   |

| 44c | TTx Valid to BCLK (Setup)                                       | 7.5    |        | 6   | _       | 8.5  | appropriate . | ns   |

| 44d | R/W Valid to BCLK (Setup)                                       | 7.7    | _      | 6   | _       | 5    | -             | ns   |

| 44e | SCx Valid to BCLK (Setup)                                       | 12.5   | _      | 10  | _       | 11   |               | ns   |

| 45  | BCLK to Address SIZx, TTx, R/W, SCx Invalid (Hold)              | 2.5    |        | 2   | erroren | 2    | _             | ns   |

| 46  | TS Valid to BCLK (Setup)                                        | 6      | _      | 5   | _       | 9    |               | ns   |

| 47  | BCLK to TS Invalid (Hold)                                       | 2.5    | _      | 2   | _       | 2    | _             | ns   |

| 49  | BCLK to BB High Impedance<br>(MC68LC040 Assumes Bus Mastership) | MARKA. | 11     | _   | 9       | _    | 9             | ns   |

| 51  | RSTI Valid to BCLK                                              | 6      | _      | 5   |         | 4    | _             | ns   |

| 52  | BCLK to RSTI Invalid                                            | 2.5    |        | 2   |         | 2    | _             | ns   |

### 11.4 MC68EC040 ELECTRICAL CHARACTERISTICS

The following paragraphs provide information on the maximum rating and thermal characteristics for the MC68EC040. This section is subject to change. For the most recent specifications, contact a Motorola sales office or complete the registration card at the beginning of this manual.

## MC68EC040 Maximum Ratings

| Characteristic                         | Symbol           | Value        | Unit |

|----------------------------------------|------------------|--------------|------|

| Supply Voltage                         | Vcc              | -0.3 to +7.0 | ٧    |

| Input Voltage                          | V <sub>in</sub>  | -0.8 to +7.0 | ٧    |

| Maximum Operating Junction Temperature | TJ               | 110          | °C   |

| Minimum Operating Ambient Temperature  | TA               | 0            | °C   |

| Storage Temperature Range              | T <sub>stg</sub> | -55 to 150   | °C   |

## MC68EC040 Thermal Characteristics PGA Package

| ļ | Characteristic                       | Symbol | Value | Rating |

|---|--------------------------------------|--------|-------|--------|

|   | Thermal Resistance, Junction to Case | θJC    | 3     | °C/W   |

## MC68EC040 DC Electrical Specifications (V<sub>CC</sub> = 5.0 Vdc ±5 %)

| Characteristic                                                                                                                      | Symbol          | Min   | Max   | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------|-------|------|

| Input High Voltage                                                                                                                  | VIH             | 2     | Vcc   | V    |

| Input Low Voltage                                                                                                                   | VIL             | GND   | 0.8   | ٧    |

| Undershoot                                                                                                                          |                 | _     | 0.8   |      |

| Input Leakage Current @ 0.52.4 V<br>AVEC, BCLK, BG, CDIS IPLx, PCLK, RSTI, SCx, TBI,<br>TLNx, TCI, TCK, TEA                         | lin             | 20    | 20    | mA   |

| Hi-Z (Off-State) Leakage Current @ 0.5–2.4 V<br>An, BB, CIOUT, Dn, LOCK, LOCKE, RW, SIZx, TA, TDO, TIP,<br>TMx, TLNx, TS, TTx, UPAx | ITSI            | 20    | 20    | mA   |

| Signal Low Input Current, V <sub>IL</sub> = 0.8 V<br>TMS, TDI, TRST                                                                 | lil             | -1.1  | -0.18 | mA   |

| Signal High Input Current, V <sub>IH</sub> = 2.0 V<br>TMS, TDI, TRST                                                                | IIH             | -0.94 | -0.16 | mA   |

| Output High Voltage, I <sub>OH</sub> = 5 mA                                                                                         | Voн             | 2.4   |       | V    |

| Output Low Voltage, IOL = 5 mA                                                                                                      | VOL             | _     | 0.5   | V    |

| Capacitance*, V <sub>in =</sub> 0 V, f = 1 MHz                                                                                      | C <sub>in</sub> |       | 25    | pF   |

<sup>\*</sup>Capacitance is periodically sampled rather than 100% tested.

MOTOROLA M68040 USER'S MANUAL 11-19

## MC68EC040 Power Dissipation

| Frequency                      | Watts                  |

|--------------------------------|------------------------|

| Maximum Values (V              | CC = 5.25 V, TA = 0°C) |

| 20 MHz                         | 4.0                    |

| 25 MHz                         | 5.0                    |

| 33 MHz                         | 6.3                    |

| Typical Values (V <sub>C</sub> | C = 5 V, TA = 25°C)*   |

| 20 MHz                         | 3.0                    |

| 25 MHz                         | 3.8                    |

| 33 MHz                         | 4.8                    |

<sup>\*</sup>This information is for system reliability purposes.

## MC68EC040 Clock AC Timing Specifications (see Figure 11-12)

|     |                                         | 20    | MHz  | 25    | MHz  | 33 MHz |       |      |

|-----|-----------------------------------------|-------|------|-------|------|--------|-------|------|

| Num | Characteristic                          | Min   | Max  | Min   | Max  | Min    | Max   | Unit |

|     | Frequency of Operation                  | 16.67 | 20   | 16.67 | 25   | 16.67  | 33.3  | MHz  |

| 1   | PCLK Cycle Time                         | 25    | 30   | 20    | 30   | 15     | 30    | ns   |

| 2   | PCLK Rise Time                          |       | 1.7  | _     | 1.7  | _      | 1.7   | ns   |

| 3   | PCLK Fall Time                          | _     | 1.6  |       | 1.6  | _      | 1.6   | ns   |

| 4   | PCLK Duty Cycle Measured at 1.5 V       | 48    | 52   | 47.5  | 52.5 | 46.67  | 53.33 | %    |

| 4a* | PCLK Pulse Width High Measured at 1.5 V | 12    | 13   | 9.5   | 10.5 | 7      | 8     | ns   |

| 4b* | PCLK Pulse Width Low Measured at 1.5 V  | 12    | 13   | 9.5   | 10.5 | 7      | 8     | ns   |

| 5   | BCLK Cycle Time                         | 50    | 60   | 40    | 60   | 30     | 60    | ns   |

| 6,7 | BCLK Rise and Fall Time                 |       | 4    | _     | 4    |        | 3     | ns   |

| 8   | BCLK Duty Cycle Measured at 1.5 V       | 40    | 60   | 40    | 60   | 40     | 60    | %    |

| 8a* | BCLK Pulse Width High Measured at 1.5 V | 20    | 30   | 16    | 24   | 12     | 18    | ns   |

| 8b* | BCLK Pulse Width Low Measured at 1.5 V  | 20    | 30   | 16    | 24   | 12     | 18    | ns   |

| 9   | PCLK, BCLK Frequency Stability          |       | 1000 |       | 1000 | _      | 1000  | ppm  |

| 10  | PCLK to BCLK Skew                       |       | 9    | _     | 9    | _      | n/a   | ns   |

<sup>\*</sup>Specification value at maximum frequency of operation.

# MC68EC040 Output AC Timing Specifications (see Figures 11-13\*-11-17)

|     |                                                                                         | 20 1 | 20 MHz |     | VIHz | 33 MHz |     |      |

|-----|-----------------------------------------------------------------------------------------|------|--------|-----|------|--------|-----|------|

| Num | Characteristic                                                                          | Min  | Max    | Min | Max  | Min    | Max | Unit |

| 11  | BCLK to Address CIOUT, LOCK, LOCKE, R/W, SIZx, TLNx,TMx, TTx, UPAx Valid                | 11.5 | 35     | 9   | 30   | 6.5    | 25  | ns   |

| 12  | BCLK to Output Invalid (Output Hold)                                                    | 11.5 | _      | 9   | _    | 6.5    |     | ns   |

| 13  | BCLK to TS Valid                                                                        | 11.5 | 35     | 9   | 30   | 6.5    | 25  | ns   |

| 14  | BCLK to TIP Valid                                                                       | 11.5 | 35     | 9   | 30   | 6.5    | 25  | ns   |

| 18  | BCLK to Data-Out Valid                                                                  | 11.5 | 37     | 9   | 32   | 6.5    | 27  | ns   |

| 19  | BCLK to Data-Out Invalid (Output Hold)                                                  | 11.5 | _      | 9   | _    | 6.5    | _   | ns   |

| 20  | BCLK to Output Low Impedance                                                            | 11.5 | _      | 9   | _    | 6.5    |     | ns   |

| 21  | BCLK to Data-Out High Impedance                                                         | 11.5 | 25     | 9   | 20   | 6.5    | 17  | ns   |

| 38  | BCLK to Address, CIOUT, LOCK, LOCKE, R/W, SIZx, TS, TLNx, TMx, TTx, UPAx High Impedance | 11.5 | 23     | 9   | 18   | 6.5    | 15  | ns   |

| 39  | BCLK to BB, TA, TIP High Impedance                                                      | 23   | 33     | 19  | 28   | 14     | 25  | пѕ   |

| 40  | BCLK to BR, BB Valid                                                                    | 11.5 | 35     | 9   | 30   | 6.5    | 23  | ns   |

| 43  | BCLK to Mi Valid                                                                        | 11.5 | 35     | 9   | 30   | 6.5    | 25  | ns   |

| 48  | BCLK to TA Valid                                                                        | 11.5 | 35     | 9   | 30   | 6.5    | 25  | ns   |

| 50  | BCLK to IPEND, PSTx, RSTO Valid                                                         | 11.5 | 35     | 9   | 30   | 6.5    | 25  | ns   |

<sup>\*</sup>Output timing is specified for a valid signal measured at the pin. Timing is specified driving an unterminated  $30-\Omega$  transmission line with a length characterized by a 2.5-ns one-way propagation delay. Buffer output impedance is typically  $30~\Omega$ ; the buffer specifications include approximately 5 ns for the signal to propagate the length of the transmission line and back.

MOTOROLA M68040 USER'S MANUAL 11-21

# MC68EC040 Input AC Timing Specifications (see Figures 11-14–11-17)

|     |                                                                 | 20   | MHz | 25  | MHz | 33  | MHz  |      |

|-----|-----------------------------------------------------------------|------|-----|-----|-----|-----|------|------|

| Num | Characteristic                                                  | Min  | Max | Min | Max | Min | Max  | Unit |

| 15  | Data-In Valid to BCLK (Setup)                                   | 6    |     | 5   | _   | 4   |      | ns   |

| 16  | BCLK to Data-In Invalid (Hold)                                  | 5    |     | 4   | _   | 4   | _    | ns   |

| 17  | BCLK to Data-In High Impedance<br>(Read Followed by Write)      |      | 61  | _   | 49  |     | 36.5 | ns   |

| 22a | TA Valid to BCLK (Setup)                                        | 12.5 | -   | 10  | _   | 10  | _    | ns   |

| 22b | TEA Valid to BCLK (Setup)                                       | 12.5 | _   | 10  |     | 10  | _    | ns   |

| 22c | TCI Valid to BCLK (Setup)                                       | 12.5 | _   | 10  |     | 10  | _    | ns   |

| 22d | TBI Valid to BCLK (Setup)                                       | 14   | _   | 11  |     | 10  |      | ns   |

| 23  | BCLK to TA, TEA, TCI, TBI Invalid (Hold)                        | 2.5  | _   | 2   |     | 2   | _    | ns   |

| 24  | AVEC Valid to BCLK (Setup)                                      | 6    | _   | 5   | _   | 5   | _    | ns   |

| 25  | BCLK to AVEC invalid (Hold)                                     | 2.5  |     | 2   |     | 2   | _    | ns   |

| 41a | BB Valid to BCLK (Setup)                                        | 8    |     | 7   |     | 7   | _    | ns   |

| 41b | BG Valid to BCLK (Setup)                                        | 10   | _   | 8   | _   | 7   | _    | ns   |

| 41c | CDIS Valid to BCLK (Setup)                                      | 12.5 | _   | 10  |     | 8   | _    | ns   |

| 41d | IPLx Valid to BCLK (Setup)                                      | 5    | _   | 4   |     | 3   |      | ns   |

| 42  | BCLK to BB, BG, CDIS, IPLx Invalid (Hold)                       | 2.5  | _   | 2   | _   | 2   | -    | ns   |

| 44a | Address Valid to BCLK (Setup)                                   | 10   | _   | 8   |     | 7   | _    | ns   |

| 44b | SIZx Valid to BCLK (Setup)                                      | 15   | _   | 12  |     | 8   | _    | ns   |

| 44c | TTx Valid to BCLK (Setup)                                       | 7.5  |     | 6   |     | 8.5 |      | ns   |

| 44d | R/W Valid to BCLK (Setup)                                       | 7.7  | _   | 6   |     | 5   | _    | ns   |

| 44e | SCx Valid to BCLK (Setup)                                       | 12.5 |     | 10  |     | 11  | _    | ns   |

| 45  | BCLK to Address SIZx, TTx, R/W, SCx<br>Invalid (Hold)           | 2.5  | _   | 2   | _   | 2   | _    | ns   |

| 46  | TS Valid to BCLK (Setup)                                        | 6    | _   | 5   |     | 9   | _    | ns   |

| 47  | BCLK to TS Invalid (Hold)                                       | 2.5  | _   | 2   | _   | 2   |      | ns   |

| 49  | BCLK to BB High Impedance<br>(MC68EC040 Assumes Bus Mastership) |      | 11  | _   | 9   | _   | 9    | ns   |

| 51  | RSTI Valid to BCLK                                              | 6    | _   | 5   |     | 4   | _    | ns   |

| 52  | BCLK to RSTI Invalid                                            | 2.5  |     | 2   |     | 2   | _    | ns   |

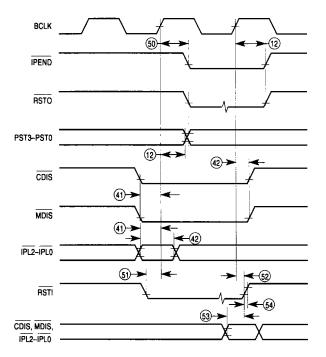

Figure 11-12. Clock Input Timing Diagram

NOTE:  $\underbrace{Transfer}_{LOCKE}$ ,  $\underbrace{Attribute}_{CIOUT}$  Signals = UPAx, SIZx, TTx, TMx, TLNx, R, $\overline{W}$ ,  $\overline{LOCK}$ ,

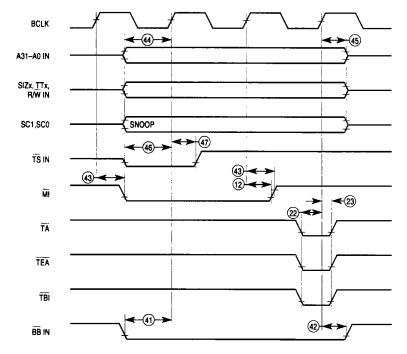

Figure 11-13. Read/Write Timing

NOTE: Transfer Attribute Signals = UPAx, SIZx, TTx, TMx, TLNx, R/W, CIOUT

Figure 11-14. Bus Arbitration Timing

Figure 11-15. Snoop Hit Timing

Figure 11-16. Snoop Miss Timing

Figure 11-17. Other Signal Timing

#### 11.5 MC68040 THERMAL DEVICE CHARACTERISTICS

The need to efficiently cool microprocessors is becoming more important as they become more complex and require more power. In the past, the M68000 family has been able to provide a 0–70°C ambient temperature part for speeds less than 40 MHz. However, the MC68040, MC68LC040, and MC68EC040 with a 50 MHz processor clock has a maximum power dissipation for a particular operating mode, a maximum junction temperature, and a thermal resistance from the die junction to the case. This provides a more accurate method of evaluating the environment, taking into consideration both the airflow and ambient temperature. This also gives the user information to design a cooling method that meets both thermal performance requirements and constraints of the board environment. This section discusses the device characteristics and several methods for thermal management as well as an example of one method for cooling the MC68040, MC68LC040, and MC68EC040. The MC68040, MC68LC040, and MC68EC040 contain inherent characteristics that should be considered when evaluating a method for cooling the device. The following paragraphs discuss these die/package and power considerations for each of these parts.

#### NOTE

All references to the MC68040 also include the MC68LC040 and MC68EC040. Note that the MC68LC040 and MC68EC040 only implement the small buffer mode.

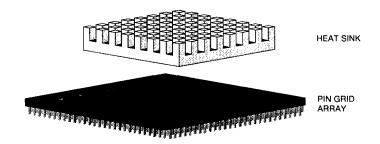

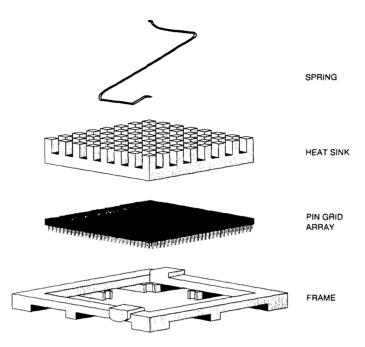

## 11.5.1 MC68040 Die and Package

The MC68040 is in a cavity-down alumina-ceramic 179-pin PGA that has a worst case thermal resistance from junction to case of 3°C/W. The package differs from previous M68000 family PGA packages that are cavity-up. The cavity-down design allows the die to be attached to the top surface of the package, increasing the part's ability to dissipate heat through the package surface or an attached heat sink. The system designer needs to determine the specific dimensions and design of the particular heat sink, considering both thermal performance and size requirements.

#### 11.5.2 MC68040 Power Considerations

The MC68040 has a maximum power rating, which varies depending on the combination of output buffer mode and operating frequency. Note that this section assumes large buffers terminated to 2.5 V. The large buffer output mode dissipates more power than the small, and higher frequencies of operation dissipate more power than the lower frequencies.

The MC68040 allows a combination of either large or small buffers on the outputs of the miscellaneous control signals, data bus, and address bus/transfer attribute pins. The large buffers offer quicker output times, allowing for an easier logic design. However, they do so by driving about 10 times as much current as the small buffers. The designer should consider whether the quicker timings present enough advantage to justify the additional consideration to the individual signal terminations, the die power consumption, and the required cooling for the device. Since the MC68040 can be powered up in one of many output buffer modes upon reset, the actual maximum power consumption for an MC68040

rated at a particular maximum operating frequency is dependent upon the power-up mode. Therefore, the MC68040 is rated at a maximum power dissipation for either the large or small buffers at a particular frequency. This allows for control of some of the thermal management upon reset. The following equation provides a rough method to calculate the maximum power consumption for a chosen output buffer mode:

$$P_D = P_{DSB} + (P_{DLB} - P_{DSB}) \times (PINS_{LB} + PINS_{CLB})$$

where:

P<sub>D</sub> = Maximum Power Dissipation for Output Buffer Mode Selected

P<sub>DSB</sub> = Maximum Power Dissipation for Small Buffer Mode (All Outputs)

P<sub>DLB</sub> = Maximum Power Dissipation for Large Buffer Mode (All Outputs)

PINS<sub>LB</sub> = Number of Pins Large Buffer Mode

PINS<sub>CLB</sub> = Number of Pins Capable of the Large Buffer Mode

Table 11-1 lists the simplified relationship on the maximum power dissipation for eight possible configurations of output buffer modes.

Table 11-1. Maximum Power Dissipation for Output Buffer Mode Configurations

|          | Output Configuration                   |                 |                                                                  |

|----------|----------------------------------------|-----------------|------------------------------------------------------------------|

| Data Bus | Address Bus and<br>Transfer Attributes | Control Signals | Maximum Power Dissipation                                        |

| Small*   | Small                                  | Small           | P <sub>DSB</sub>                                                 |

| Small    | Small                                  | Large           | P <sub>DSB</sub> + (P <sub>DLB</sub> - P <sub>DSB</sub> ) × 13%  |

| Small    | Large                                  | Small           | P <sub>DSB</sub> + (P <sub>DLB</sub> ~ P <sub>DSB</sub> ) × 52%  |

| Small    | Large                                  | Large           | P <sub>DSB</sub> + (P <sub>DLB</sub> - P <sub>DSB</sub> ) × 65%  |

| Large    | Small                                  | Small           | P <sub>DSB</sub> + (P <sub>DLB</sub> - P <sub>DSB</sub> ) × 35%  |

| Large    | Small                                  | Large           | P <sub>DSB</sub> + (P <sub>DLB</sub> - P <sub>DSB</sub> ) × 48%  |

| Large    | Large                                  | Small           | P <sub>DSB</sub> + (P <sub>DLB</sub> - P <sub>DSB</sub> ) ×87%   |

| Large    | Large                                  | Large           | P <sub>DSB</sub> + (P <sub>DLB</sub> - P <sub>DSB</sub> ) × 100% |

<sup>\*</sup>The MC68LC040 and MC68EC040 only utilize this row of information.

To calculate the specific power dissipation of a design, the termination method of each signal must be considered. For example, a signal output that is not connected would not dissipate any additional power if it were configured in the large rather than the small buffer mode. Since the maximum operating junction temperature is specified as 110°C, the maximum case temperature (T<sub>C</sub>) in °C can be obtained from the following equation:

$$T_C = T_A - P_D \times \theta_{AC}$$

where:

T<sub>C</sub> = Maximum Case Temperature

$T_J$  = Maximum Junction Temperature

P<sub>D</sub> = Maximum Power Dissipation of the Device

$\theta_{JC}$  = Thermal Resistance between the Junction of the Die and the Case

In general, the ambient temperature (T<sub>A</sub>) in °C is a function of the following equation:

$$T_A = T_J - P_D \times \theta_{JC} - P_D \times \theta_{CA}$$

The thermal resistance from case to outside ambient  $(\theta_{CA})$  is the only user-dependent parameter once a buffer output configuration has been determined. Reducing the case to ambient thermal resistance increases the maximum operating ambient temperature. Therefore, by utilizing methods such as heat sinks and ambient air cooling to minimize  $\theta_{CA}$ , a higher ambient operating temperature and/or a lower junction temperature can be achieved. However, an easier approach to thermal evaluation uses the following equations:

$$T_A = T_J - P_{D \times} \theta_{JA}$$

or  $T_J = T_A + P_{D \times} \theta_{JA}$

where:

$\theta_{JA}$  = Thermal Resistance from the Junction to the Ambient ( $\theta_{JC} + \theta_{CA}$ )

The total thermal resistance for a package  $(\theta_{JA})$  is a combination of its two components,  $\theta_{JC}$  and  $\theta_{CA}$ . These components represent the barrier to heat flow from the semiconductor junction to the package case surface  $(\theta_{JC})$  and  $\theta_{CA}$ . Although  $\theta_{JC}$  is package related and the user cannot influence it,  $\theta_{CA}$  is user dependent. Good thermal management by the user, such as heat sink and airflow, can significantly reduce  $\theta_{CA}$  achieving either a lower semiconductor junction temperature or a higher ambient operating temperature.

## 11.6 THERMAL MANAGEMENT TECHNIQUES

To attain a reasonable maximum ambient operating temperature, the user must reduce the barrier to heat flow from  $\theta_{JA}$ . The only way to accomplish this is to significantly reduce  $\theta_{CA}$  by applying thermal management techniques such as heat sinks and forced air cooling. The following paragraphs discuss thermal study results for the MC68040 that did not use thermal management techniques, airflow cooling, heat sink, and heat sink combined with airflow cooling.

The MC68040 power dissipation values given in this section represent the sum of the power dissipated by the internal circuitry and the output buffers of the MC68040. The termination network chosen by the system designer strongly influences this last component of power. Values listed in this section for large buffer terminated entries reflect a termination network as illustrated in Figure 11-18 and are consistent with specifications for the MC68040. For additional termination schemes, refer to AN1051, *Transmission Line Effects in PCB Applications*, or AN1061, *Reflecting on Transmission Line Effects*.

Figure 11-18. MC68040 Termination Network

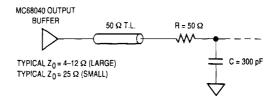

If a designer uses alternative standard termination methods, such as RC termination network (see Figure 11-19), Thévenin termination network (not illustrated), or no termination method at all, which is not recommended, then the power dissipation of the MC68040 will be significantly less than the large buffer terminated values. For termination networks other than that illustrated in Figure 11-19, the designer must calculate the component of power dissipated in the output buffer and add this value to the small buffer unterminated value.

Figure 11-19 Typical Configuration for RC Termination Network

The following paragraphs describe how the large buffer terminated values were calculated. The MC68040 termination network causes current flow through the output buffer of the MC68040, regardless of whether the MC68040 is driving a logic one or a logic zero. The following equation gives the large buffer termination network power dissipation for a given pin:

$$I = (V + (R + Z_0)) + 5 \text{ mA}$$

$P = I^2 R_{eff}$

R<sub>eff</sub> is the effective average output resistance, including typical pullup resistance, typical pulldown resistance, and a duty cycle average of how often the pin is high, low, or three-stated. Typical values for  $Z_0$  are 6  $\Omega$  for large buffer low output, 12  $\Omega$  for large buffer high output, and 25  $\Omega$  for small buffer output. Using these values and duty cycle assumptions based on sequential burst write cycles, R<sub>eff</sub> calculates to 7.7  $\Omega$  for the MC68040 large buffer mode and 25  $\Omega$  for the small buffer mode.

Maximum termination current in the large buffer mode occurs for output:

Low:

$$I_{11} = (2.5 \text{ V} + (50 + 6 \Omega)) + 5 \text{ mA} = 49.6 \text{ mA}$$

High:  $I_{1th} = (2.75 \text{ V} + (50 + 12 \Omega)) + 5 \text{ mA} = 50.8 \text{ mA}$

11-32 M68040 USER'S MANUAL MOTOROLA

11-33

Maximum power dissipation in the large buffer mode occurs for output:

Low:

$$P_{IIb} = I^2R = (49.6 \text{ mA})^2 \times 6 \Omega = 14.8 \text{ mW}$$

High:  $P_{hIb} = I^2R = (50.8 \text{ mA})^2 \times 12 \Omega = 30.1 \text{ mW}$

Similar calculations for unterminated small buffers yield:

$$I = 5 \text{ mA (by spec)}$$

and

$$P = I^2R = (5 \text{ mA})^2 \times 25 \Omega$$

SO

$$P_{hsb} = 0.625 \text{ mW}$$

$P_{lsb} = 0.625 \text{ mW}$

Assuming that the duty cycle of output j is driving a valid logic value instead of being three-stated as given by DCj, then the following equation approximates total average power dissipation in the output buffers:

Number of Outputs Used

$$I_{Total} = \sum_{j=1}^{N} (I_j \times DC_j)^2 \times R_{effj}$$

$I_j$  and  $Z_{0j}$  are calculated for every pin as illustrated above. In practice the above summation is carried out by groups of pins instead of individual pins.

Motorola has calculated the values for  $DC_j$  for typical situations. On an average clock there will be 37.8 pins high, 41.5 pins low, and 11.7 pins three-stated. The following examples demonstrate how to calculate the power dissipation that is added to small buffer power dissipation numbers, assuming a termination as illustrated in Figure 11-18.

- a. For the numbers listed in this section in a large buffer design with no caching.

- $P = (Number of Pins High) \times (P_{hlb}) + (Number of Pins Low) \times (P_{llb})$

- = 37.8 Pins × 30.1 mW per Pin + 41.5 Pins × 14.8 mW per Pin

- = 1.75 W

- b. For a single bus master system in a large buffer design with no caching or snooping and only standard features (i.e., TLN, UPA, BR, BB, LOCK, LOCKE, CIOUT, TIP, MI, TDO, IPEND, PST not used):

- P = (Number of Pins High)  $\times$  (P<sub>hlb</sub>) + (Number of Pins Low)  $\times$  (P<sub>llb</sub>)

- = 29.8 Pins × 30.1 mW per Pin + 34.5 Pins × 14.8 mW per Pin

- = 1.41 W

- c. For the example b system with copyback caching, assuming 85% cache hit rate:

- $P = (29.8 \text{ Pins} \times 30.1 \text{ mW per Pin} + 34.5 \text{ Pins} \times 14.8 \text{ mW per Pin}) \times (1 0.85)$ = 0.21 W

MOTOROLA M68040 USER'S MANUAL

- d. For the example c system running the data bus in small buffer mode with other outputs in large buffer mode terminated:

- P = (Number of Pins Large Buffer High)  $\times$  (Phlb) + (Number of Pins Large Buffer Low)  $\times$  (Pllb) + (Number of Pins Small Buffer High)  $\times$  (Phsb) + (Number of Pins Small Buffer Low)  $\times$  (Plsb)

- = 19.1 Pins  $\times$  30.1 mW per Pin + 23.8 Pins  $\times$  14.8 mW per Pin + 10.7 Pins  $\times$  0.625 mW per Pin + 10.7 Pins  $\times$  0.625 mW per Pin

- $= 0.94 \text{ W} \times (1 0.85)$

- = 0.14 W

#### 11.6.1 MC68040 Thermal Characteristics in Still Air

In this study, a small sample of MC68040 packages was tested in free-air cooling with no heat sink. Measurements showed that the average  $\theta_{JA}$  was 22.8°C/W with a standard deviation of 0.44°C/W. The test was performed with approximately 6 W of power being dissipated from within the package. The test determined that  $\theta_{JA}$  decreases slightly for the increasing power dissipation range possible. Therefore, since the variance in  $\theta_{JA}$  within the possible power dissipation range is negligible, it can be assumed for calculation purposes that  $\theta_{JA}$  is valid at all power levels. Using the previous equations, Table 11-2 lists the results of a maximum power dissipation at maximum  $\theta_{JC}$  with no heat sink or airflow (see Table 11-1 to calculate other power dissipation values). The ambient temperature results illustrate the need to implement some type of thermal management to obtain a reasonable maximum ambient temperature.

Table 11-2. Thermal Parameters with No Heat Sink or Airflow

|     | Defined Parameters      |        |     | Measured |                                               | Calculated                                   |                                                                                  |  |  |  |

|-----|-------------------------|--------|-----|----------|-----------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------|--|--|--|

| MHz | PD                      | TJ     | θлс | θJA      | $\theta_{CA}$ ( $\theta_{JA} - \theta_{JC}$ ) | $T_{C}$ $(T_{J} - P_{D} \times \theta_{JC})$ | $T_{\mathbf{A}}$ $(\mathbf{T_{J}} - \mathbf{P_{D}} \times \theta_{\mathbf{JA}})$ |  |  |  |

|     | MC68040                 |        |     |          |                                               |                                              |                                                                                  |  |  |  |

| 25  | 6.3                     | 110 °C | 3   | 22.8     | 19.8                                          | 91.1                                         | -33.64                                                                           |  |  |  |

| 25  | 6.6                     | 110 °C | 3   | 22.8     | 19.8                                          | 90.2                                         | -40.48                                                                           |  |  |  |

| 25  | 8.6                     | 110 °C | 3   | 22.8     | 19.8                                          | 84.2                                         | -86.08                                                                           |  |  |  |

| 33  | 7.7                     | 110 °C | 3   | 22.8     | 19.8                                          | 86.9                                         | -65.56                                                                           |  |  |  |

| 33  | 8.0                     | 110 °C | 3   | 22.8     | 19.8                                          | 86.0                                         | -72.40                                                                           |  |  |  |

| 33  | 10.0                    | 110 °C | 3   | 22.8     | 19.8                                          | 80.0                                         | -118.00                                                                          |  |  |  |

|     | MC68LC040 and MC68EC040 |        |     |          |                                               |                                              |                                                                                  |  |  |  |

| 20  | 4                       | 110 °C | 3   | 22.8     | 19.8                                          | 98                                           | 18.8                                                                             |  |  |  |

| 25  | 5                       | 110 °C | 3   | 22.8     | 19.8                                          | 95                                           | -4                                                                               |  |  |  |

| 33  | 6.3                     | 110 °C | 3   | 22.8     | 19.8                                          | 91.1                                         | -33.64                                                                           |  |  |  |

11-34 M68040 USER'S MANUAL MOTOROLA

### 11.6.2 MC68040 Thermal Characteristics in Forced Air

In this study, a small sample of MC68040 packages was tested in forced-air cooling in a wind tunnel with no heat sink. The test was performed with approximately 6 W of power being dissipated from within the package. As previously mentioned, since the variance in  $\theta_{JA}$  within the possible power range is negligible, it can be assumed for calculation purposes that  $\theta_{JA}$  is constant at all power levels. Using the previous equations, Table 11-3 lists the results of the maximum power dissipation at maximum  $\theta_{JC}$  with airflow and no heat sink for the MC68040, and Table 11-4 lists the results for the MC68LC040 and MC68EC040. Refer to Table 11-1 for calculating other power dissipation values.

Table 11-3. Thermal Parameters with Forced Airflow and No Heat Sink for the MC68040

|                                  | Thermal Mgmt.<br>Technique | Defined Parameters                                  |        |        | Measured  | Calculated |                                                                |                                                                      |

|----------------------------------|----------------------------|-----------------------------------------------------|--------|--------|-----------|------------|----------------------------------------------------------------|----------------------------------------------------------------------|

| MHz                              | Airflow Velocity           | P <sub>D</sub>                                      | TJ     | θJC    | ALθ       | θCA        | T <sub>C</sub>                                                 | TA                                                                   |

| 25<br>25<br>25<br>33<br>33<br>33 | 100 LFM                    | 6.3 W<br>6.6 W<br>8.6 W<br>7.7 W<br>8.0 W<br>10.0 W | 110 °C | 3 °C/W | 12.7 °C/W | 9.7 °C/W   | 91.1 °C<br>90.2 °C<br>84.9 °C<br>86.9 °C<br>86.0 °C<br>80.0 °C | 29.90 °C<br>26.18 °C<br>00.76 °C<br>12.21 °C<br>08.40 °C<br>00.00°C  |

| 25<br>25<br>25<br>33<br>33<br>33 | 250 LFM                    | 6.3 W<br>6.6 W<br>8.6 W<br>7.7 W<br>8.0 W<br>10.0 W | 110 °C | 3 °C/W | 11.0 °C/W | 8.0 °C/W   | 91.1 °C<br>90.2 °C<br>84.2 °C<br>86.9 °C<br>86.0 °C<br>80.0 °C | 40.70 °C<br>37.40 °C<br>15.40 °C<br>25.30 °C<br>22.00 °C<br>00.00 °C |

| 25<br>25<br>25<br>33<br>33<br>33 | 500 LFM                    | 6.3 W<br>6.6 W<br>8.6 W<br>7.7 W<br>8.0 W<br>10.0 W | 110 °C | 3 °C/W | 9.9 °C/W  | 6.9 °C/W   | 91.1 °C<br>90.2 °C<br>84.2 °C<br>86.9 °C<br>86.0 °C<br>80.0 °C | 47.63 °C<br>44.66 °C<br>24.86 °C<br>33.77 °C<br>30.80 °C<br>11.00 °C |

| 25<br>25<br>25<br>33<br>33<br>33 | 750 LFM                    | 6.3 W<br>6.6 W<br>8.6 W<br>7.7 W<br>8.0 W<br>10.0 W | 110 °C | 3 °C/W | 9.5 °C/W  | 6.5 °C/W   | 91.1 °C<br>90.2 °C<br>84.2 °C<br>86.9 °C<br>86.0 °C<br>80.0 °C | 50.15 °C<br>47.30 °C<br>28.30 °C<br>36.85 °C<br>34.00 °C<br>15.00 °C |

| 25<br>25<br>25<br>33<br>33<br>33 | 1000 LFM                   | 6.3 W<br>6.6 W<br>8.6 W<br>7.7 W<br>8.0 W<br>10.0 W | 110 °C | 3 °C/W | 9.3 °C/W  | 6.3 °C/W   | 91.1 °C<br>90.2 °C<br>84.2 °C<br>86.9 °C<br>80.0 °C<br>81.8 °C | 51.41 °C<br>48.62 °C<br>30.02 °C<br>38.39 °C<br>17.00 °C<br>22.58 °C |

Table 11-4. Thermal Parameters with Forced Airflow and No Heat Sink for the MC68LC040 and MC68EC040

|                | Thermal Mgmt.<br>Technique | De                 | fined Parame | eters  | Measured        | Calculated |                           |                                |

|----------------|----------------------------|--------------------|--------------|--------|-----------------|------------|---------------------------|--------------------------------|

| MHz            | Airflow Velocity           | PD                 | Tj           | θJC    | θ <sub>JA</sub> | θCA        | τ <sub>c</sub>            | TA                             |

| 20<br>25<br>33 | 100 LFM                    | 4 W<br>5 W<br>6.3W | 110 °C       | 3 °C/W | 12.7 °C/W       | 9.7 °C/W   | 98 °C<br>95 °C<br>91.1 °C | 59.2 °C<br>46.5 °C<br>29.9 °C  |

| 20<br>25<br>33 | 250 LFM                    | 4 W<br>5 W<br>6.3W | 110 °C       | 3 °C/W | 11 °C/W         | 8 °C/W     | 98 °C<br>95 °C<br>91.1 °C | 66 °C<br>55 °C<br>40.70 °C     |

| 20<br>25<br>33 | 500 LFM                    | 4 W<br>5 W<br>6.3W | 110 °C       | 3 °C/W | 9.9 °C/W        | 6.9 °C/W   | 98 °C<br>95 °C<br>91.1 °C | 70.4 °C<br>60.5 °C<br>47.63 °C |

| 20<br>25<br>33 | 750 LFM                    | 4 W<br>5 W<br>6.3W | 110 °C       | 3 °C/W | 9.5 °C/W        | 6.5 °C/W   | 98 °C<br>95 °C<br>91.1 °C | 72 °C<br>62.5 °C<br>50.15 °C   |

| 20<br>25<br>33 | 1000 LFM                   | 4 W<br>5 W<br>6.3W | 110 °C       | 3 °C/W | 9.3 °C/W        | 6.3 °C/W   | 98 °C<br>95 °C<br>91.1 °C | 72.8 °C<br>63.5 °C<br>51.41 °C |

Reviewing the maximum ambient operating temperatures illustrates that using an all small buffer configuration of the MC68040 with a relatively small amount of airflow (100 LFM) achieves a 0–70 °C ambient operating temperature. However, depending on the output buffer configuration and available forced-air cooling, additional thermal management techniques may be required.

#### 11.6.3 MC68040 Thermal Characteristics with a Heat Sink

The designer must consider many factors in choosing a heat sink: heat-sink size and composition, method of attachment, and choice of a dry or wet (i.e., thermal grease) connection. The following paragraphs discuss the relationship of these decisions to the thermal performance of the design noticed during experimentation.