# INTEGRATED CIRCUITS

# DATA SHEET

# P5Z22V10

5V zero power, TotalCMOS™, universal PLD device

Product specification

Supersedes data of 1997 Apr 04

IC27 Data Handbook

# 5V zero power, TotalCMOS™, universal PLD device

P5Z22V10

#### **FEATURES**

- Industry's first TotalCMOS™ 22V10 both CMOS design and process technologies

- Fast Zero Power (FZP™) design technique provides ultra-low power and high speed

- Static current of less than 75µA

- Dynamic current 1/10 to 1/1000 that of competing devices

- Pin-to-pin delay of only 7.5ns

- True Zero Power device with no turbo bits or power down schemes

- Function/JEDEC map compatible with Bipolar UVCMOS EECMOS 22V10s

- Multiple packaging options featuring PCB-friendly flow-through pinouts (SOL and TSSOP)

- 24-pin TSSOP—uses 93% less in-system space than a 28-pin PLCC

- 24-pin SOL

- 28-pin PLCC with standard JEDEC pin-out

- Available in commercial and industrial operating ranges

- Advanced 0.5μ E<sup>2</sup>CMOS process

- 1000 erase/program cycles guaranteed

- 20 years data retention guaranteed

- Varied product term distribution with up to 16 product terms per output for complex functions

- Programmable output polarity

- Synchronous preset/asynchronous reset capability

- Security bit prevents unauthorized access

- Electronic signature for identification

- Design entry and verification using industry standard CAE tools

- Reprogrammable using industry standard device programmers

### **DESCRIPTION**

The P5Z22V10 is the first SPLD to combine high performance with low power, without the need for "turbo bits" or other power down schemes. To achieve this, Philips Semiconductors has used their FZP™ design technique, which replaces conventional sense amplifier methods for implementing product terms (a technique that has been used in PLDs since the bipolar era) with a cascaded chain of pure CMOS gates. This results in the combination of low power and high speed that has previously been unattainable in the PLD arena. For 3V operation, Philips Semiconductors offers the P3Z22V10 that offers high speed and low power in a 3V implementation.

The P5Z22V10 uses the familiar AND/OR logic array structure, which allows direct implementation of sum-of-products equations. This device has a programmable AND array which drives a fixed OR array. The OR sum of products feeds an "Output Macro Cell" (OMC), which can be individually configured as a dedicated input, a combinatorial output, or a registered output with internal feedback.

### ORDERING INFORMATION

| ORDER CODE   | PACKAGE      | PROPAGATION<br>DELAY | TEMPERATURE<br>RANGE | OPERATING RANGE             | DRAWING<br>NUMBER |

|--------------|--------------|----------------------|----------------------|-----------------------------|-------------------|

| P5Z22V10-7A  | 28-pin PLCC  | 7.5ns                | 0 to +70°C           | $V_{CC} = 5.0V \pm 5\%$     | SOT261-3          |

| P5Z22V10-7D  | 24-pin SOL   | 7.5ns                | 0 to +70°C           | $V_{CC} = 5.0V \pm 5\%$     | SOT137-1          |

| P5Z22V10-7DH | 24-pin TSSOP | 7.5ns                | 0 to +70°C           | $V_{CC} = 5.0V \pm 5\%$     | SOT355-1          |

| P5Z22V10-DA  | 28-pin PLCC  | 10ns                 | 0 to +70°C           | $V_{CC} = 5.0V \pm 5\%$     | SOT261-3          |

| P5Z22V10-DD  | 24-pin SOL   | 10ns                 | 0 to +70°C           | $V_{CC} = 5.0V \pm 5\%$     | SOT137-1          |

| P5Z22V10-DDH | 24-pin TSSOP | 10ns                 | 0 to +70°C           | $V_{CC} = 5.0V \pm 5\%$     | SOT355-1          |

| P5Z22V10IDA  | 28-pin PLCC  | 10ns                 | –40 to +85°C         | $V_{CC} = 5.0V \pm 10\%$    | SOT261-3          |

| P5Z22V10IDD  | 24-pin SOL   | 10ns                 | –40 to +85°C         | V <sub>CC</sub> = 5.0V ±10% | SOT137-1          |

| P5Z22V10IDDH | 24-pin TSSOP | 10ns                 | –40 to +85°C         | $V_{CC} = 5.0V \pm 10\%$    | SOT355-1          |

# 5V zero power, TotalCMOS™, universal PLD device

P5Z22V10

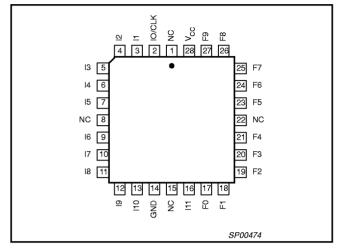

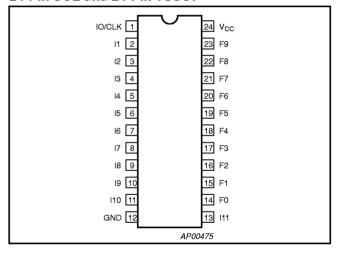

# **PIN CONFIGURATIONS**

# 28-Pin PLCC

# **PIN DESCRIPTIONS**

| PIN LABEL       | DESCRIPTION                 |

|-----------------|-----------------------------|

| l1 – l11        | Dedicated Input             |

| NC              | Not Connected               |

| F0 – F9         | Macrocell Input/Output      |

| I0/CLK          | Dedicated Input/Clock Input |

| V <sub>CC</sub> | Supply Voltage              |

| GND             | Ground                      |

# 24-Pin SOL and 24-Pin TSSOP

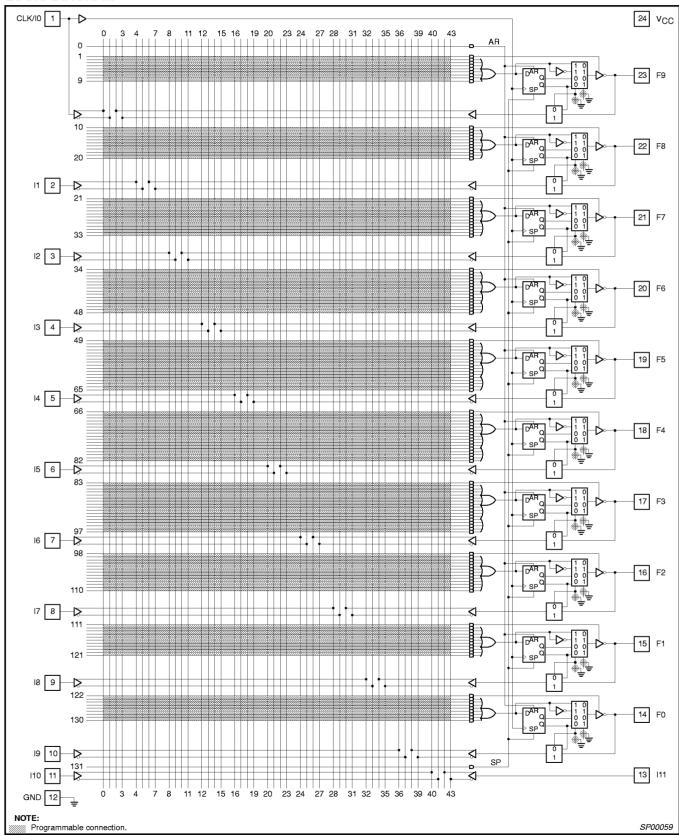

# **LOGIC DIAGRAM**

# 5V zero power, TotalCMOS™, universal PLD device

P5Z22V10

Figure 1. Functional Diagram

### **FUNCTIONAL DESCRIPTION**

The P5Z22V10 implements logic functions as sum-of-products expressions in a programmable-AND/fixed-OR logic array. User-defined functions are created by programming the connections of input signals into the array. User-configurable output structures in the form of I/O macrocells further increase logic flexibility.

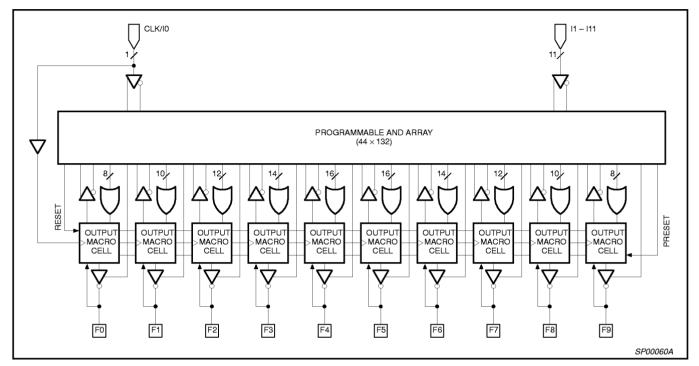

### **ARCHITECTURE OVERVIEW**

The P5Z22V10 architecture is illustrated in Figure 1. Twelve dedicated inputs and 10 I/Os provide up to 22 inputs and 10 outputs for creation of logic functions. At the core of the device is a programmable electrically-erasable AND array which drives a fixed-OR array. With this structure, the P5Z22V10 can implement up to 10 sum-of-products logic expressions.

Associated with each of the 10 OR functions is an I/O macrocell which can be independently programmed to one of 4 different configurations. The programmable macrocells allow each I/O to create sequential or combinatorial logic functions with either Active-High or Active-Low polarity.

### **AND/OR Logic Array**

The programmable AND array of the P5Z22V10 (shown in the Logic Diagram) is formed by input lines intersecting product terms. The input lines and product terms are used as follows:

#### 44 input lines:

- 24 input lines carry the True and Complement of the signals applied to the 12 input pins

- 20 additional lines carry the True and Complement values of feedback or input signals from the 10 I/Os

#### 132 product terms:

- 120 product terms (arranged in 2 groups of 8, 10, 12, 14, and 16) used to form logical sums

- 10 output enable terms (one for each I/O)

- 1 global synchronous preset product term

- 1 global asynchronous clear product term

At each input-line/product-term intersection there is an EEPROM memory cell which determines whether or not there is a logical connection at that intersection. Each product term is essentially a 44-input AND gate. A product term which is connected to both the True and Complement of an input signal will always be FALSE, and thus will not affect the OR function that it drives. When all the connections on a product term are opened, a Don't Care state exists and that term will always be TRUE.

# Variable Product Term Distribution

The P5Z22V10 provides 120 product terms to drive the 10 OR functions. These product terms are distributed among the outputs in groups of 8, 10, 12, 14, and 16 to form logical sums (see Logic Diagram). This distribution allows optimum use of device resources.

# 5V zero power, TotalCMOS™, universal PLD device

P5Z22V10

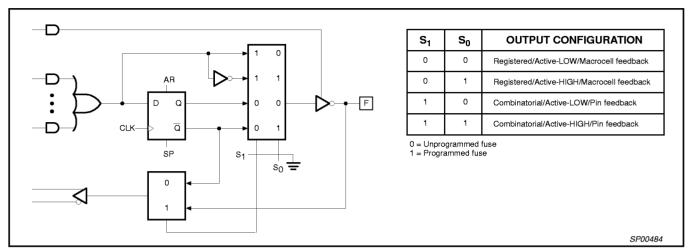

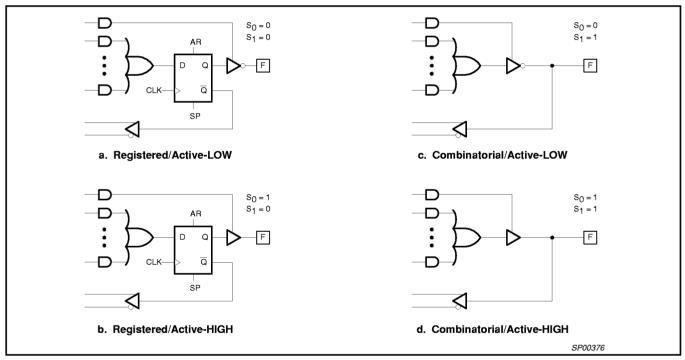

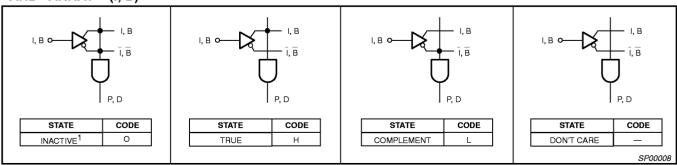

Figure 2. Output Macro Cell Logic Diagram

Figure 3. Output Macro Cell Configurations

# Programmable I/O Macrocell

The output macrocell provides complete control over the architecture of each output, the ability to configure each output independently permits users to tailor the configuration of the P5Z22V10 to the precise requirements of their designs.

# **Macrocell Architecture**

Each I/O macrocell, as shown in Figure 2, consists of a D-type flip-flop and two signal-select multiplexers. The configuration of each macrocell of the P5Z22V10 is determined by the two EEPROM bits controlling these multiplexers. These bits determine output polarity, and output type (registered or non-registered). Equivalent circuits for the macrocell configurations are illustrated in Figure 3.

# **Output type**

The signal from the OR array can be fed directly to the output pin (combinatorial function) or latched in the D-type flip-flop (registered function). The D-type flip-flop latches data on the rising edge of the clock and is controlled by the global preset and clear terms. When the synchronous preset term is satisfied, the Q output of the register will be set HIGH at the next rising edge of the clock input. Satisfying the asynchronous clear term will set Q LOW, regardless of the clock state. If both terms are satisfied simultaneously, the clear will override the preset.

# 5V zero power, TotalCMOS™, universal PLD device

P5722V10

# **Program/Erase Cycles**

The P5Z22V10 is 100% testable, erases/programs in seconds, and guarantees 1000 program/erase erase cycles.

### **Output Polarity**

Each macrocell can be configured to implement Active-High or Active-Low logic. Programmable polarity eliminates the need for external inverters.

# **Output Enable**

The output of each I/O macrocell can be enabled or disabled under the control of its associated programmable output enable product term. When the logical conditions programmed on the output enable term are satisfied, the output signal is propagated to the I/O pin. Otherwise, the output buffer is driven into the high-impedance state.

Under the control of the output enable term, the I/O pin can function as a dedicated input, a dedicated output, or a bi-directional I/O. Opening every connection on the output enable term will permanently enable the output buffer and yield a dedicated output. Conversely, if every connection is intact, the enable term will always be logically FALSE and the I/O will function as a dedicated input.

### Register Feedback Select

When the I/O macrocell is configured to implement a registered function (S1 = 0) (Figures 3a or 3b), the feedback signal to the AND array is taken from the  $\overline{Q}$  output.

### Bi-directional I/O Select

When configuring an I/O macrocell to implement a combinatorial function (S1 = 1) (Figures 3c or 3d), the feedback signal is taken from the I/O pin. In this case, the pin can be used as a dedicated input, a dedicated output, or a bi-directional I/O.

### **Power-On Reset**

To ease system initialization, all flip-flops will power-up to a reset condition and the Q output will be low. The actual output of the P5Z22V10 will depend on the programmed output polarity. The  $V_{CC}$  rise must be monotonic.

### **Design Security**

The P5Z22V10 provides a special EEPROM security bit that prevents unauthorized reading or copying of designs programmed into the device. The security bit is set by the PLD programmer, either at the conclusion of the programming cycle or as a separate step, after the device has been programmed. Once the security bit is set, it is impossible to verify (read) or program the P5Z22V10 until the entire device has first been erased with the bulk-erase function.

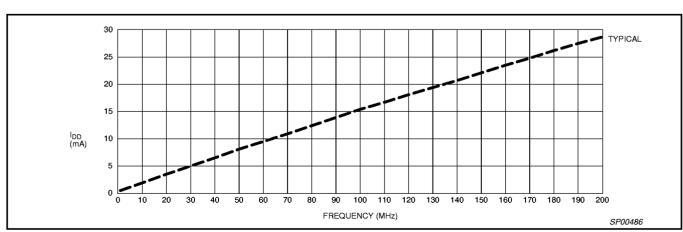

# TotalCMOS™ Design Technique for Fast Zero Power

Philips is the first to offer a TotalCMOS™ SPLD, both in process technology and design technique. Philips employs a cascade of CMOS gates to implement its Sum of Products instead of the traditional sense amp approach. This CMOS gate implementation allows Philips to offer SPLDs which are both high performance and low power, breaking the paradigm that to have low power, you must accept low performance. Refer to Figure 4 and Table 1 showing the I<sub>DD</sub> vs. Frequency of our P5Z22V10 TotalCMOS™ SPLD.

Table 1. Typical I<sub>DD</sub> vs. Frequency

$V_{DD} = 5V @ 25^{\circ}C$

| FREQUENCY (MHz) | TYPICAL I <sub>DD</sub> (mA) |

|-----------------|------------------------------|

| 1               | 0.5                          |

| 10              | 1.9                          |

| 20              | 3.5                          |

| 30              | 5.0                          |

| 40              | 6.5                          |

| 50              | 8.1                          |

| 60              | 9.5                          |

| 70              | 10.9                         |

| 80              | 12.4                         |

| 90              | 13.9                         |

| 100             | 15.4                         |

| 110             | 16.7                         |

| 120             | 18.1                         |

| 130             | 19.4                         |

| 140             | 20.7                         |

| 150             | 22.1                         |

| 160             | 23.5                         |

| 170             | 24.8                         |

| 180             | 26.2                         |

| 190             | 27.5                         |

| 200             | 28.7                         |

Figure 4. Typical I<sub>DD</sub> vs. Frequency @ V<sub>DD</sub> = 5V, 25°C (10-bit counter)

# 5V zero power, TotalCMOS™, universal PLD device

P5Z22V10

# **ABSOLUTE MAXIMUM RATINGS<sup>1</sup>**

| SYMBOL           | PARAMETER                                  | LIM  | ITS                   | UNIT |

|------------------|--------------------------------------------|------|-----------------------|------|

| STIVIDOL         | PARAMETER                                  | MIN. | MAX.                  | UNIT |

| $V_{DD}$         | Supply voltage                             | -0.5 | 7.0                   | ٧    |

| V <sub>I</sub>   | Input voltage                              | -1.2 | V <sub>DD</sub> + 0.5 | ٧    |

| V <sub>OUT</sub> | Output voltage                             | -0.5 | V <sub>DD</sub> + 0.5 | ٧    |

| I <sub>IN</sub>  | Input current                              | -30  | 30                    | mA   |

| I <sub>OUT</sub> | Output current                             | -100 | 100                   | mA   |

| T <sub>R</sub>   | Allowable thermal rise ambient to junction | 0    | 75                    | °C   |

| TJ               | Junction temperature range                 | -40  | 150                   | °C   |

| T <sub>STG</sub> | Storage temperature range                  | -65  | 150                   | °C   |

| ESD              | Static discharge voltage (human body)      |      | 1000                  | ٧    |

### NOTE:

# **OPERATING RANGE**

| PRODUCT GRADE | TEMPERATURE  | VOLTAGE           |

|---------------|--------------|-------------------|

| Commercial    | 0 to +70°C   | 5.0 ± 5% <b>V</b> |

| Industrial    | –40 to +85°C | 5.0 ± 10% V       |

<sup>1.</sup> Stresses above those listed may cause malfunction or permanent damage to the device. This is a stress rating only. Functional operation at these or any other condition above those indicated in the operational and programming specification of the device is not implied.

# 5V zero power, TotalCMOS™, universal PLD device

P5Z22V10

### DC ELECTRICAL CHARACTERISTICS FOR COMMERCIAL GRADE DEVICES

Commercial:  $0^{\circ}C \le T_{amb} \le +70^{\circ}C$ ;  $4.75 \le V_{DD} \le 5.25V$

| SYMBOL                        | PARAMETER                       | TEST CONDITIONS                                         |      | LIMITS |      | UNITS |

|-------------------------------|---------------------------------|---------------------------------------------------------|------|--------|------|-------|

| STWIDOL                       | FARAMETER                       | TEST CONDITIONS                                         | MIN. | TYP.   | MAX. | ONITS |

| V <sub>IL</sub>               | Input voltage low               | V <sub>DD</sub> = 4.75V                                 |      |        | 0.8  | ٧     |

| V <sub>IH</sub>               | Input voltage high              | V <sub>DD</sub> = 5.25V                                 | 2    |        |      | V     |

| VI                            | Input clamp voltage             | $V_{DD} = 4.75V; I_{IN} = -18mA$                        |      |        | -1.2 | ٧     |

| V <sub>OL</sub>               | Output voltage low              | $V_{DD} = 4.75V; I_{OL} = 8mA$                          |      |        | 0.5  | V     |

| V <sub>OH</sub>               | Output voltage high             | $V_{DD} = 4.75V; I_{OL} = -4mA$                         | 2.4  |        |      | V     |

| II                            | Input leakage current           | $V_{IN} = 0$ to $V_{DD}$                                | -10  |        | 10   | μΑ    |

| loz                           | 3-Stated output leakage current | $V_{IN} = 0$ to $V_{DD}$                                | -10  |        | 10   | μΑ    |

| $I_{DDQ}$                     | Standby current                 | V <sub>DD</sub> = 5.25V; T <sub>amb</sub> = 0°C         |      | 60     | 75   | μΑ    |

| I <sub>DDD</sub> <sup>1</sup> | Dynamic current                 | V <sub>DD</sub> = 5.25V; T <sub>amb</sub> = 0°C @ 1MHz  |      | 1      | 3    | mA    |

| י סססי                        | Dynamic current                 | V <sub>DD</sub> = 5.25V; T <sub>amb</sub> = 0°C @ 50MHz |      | 10     | 15   | mA    |

| I <sub>SC</sub>               | Short circuit output current    | 1 pin/time for no longer than 1 second                  | -30  |        | -100 | mA    |

| C <sub>IN</sub>               | Input pin capacitance           | T <sub>amb</sub> = 25°C; f = 1MHz                       |      |        | 10   | pF    |

| C <sub>CLK</sub>              | Clock input capacitance         | T <sub>amb</sub> = 25°C; f = 1MHz                       | 5    |        | 12   | pF    |

| C <sub>I/O</sub>              | I/O pin capacitance             | T <sub>amb</sub> = 25°C; f = 1MHz                       |      |        | 10   | pF    |

### NOTE:

### AC ELECTRICAL CHARACTERISTICS FOR COMMERCIAL GRADE DEVICES

Commercial:  $0^{\circ}C \le T_{amb} \le +70^{\circ}C$ ;  $4.75 \le V_{DD} \le 5.25V$

| SYMBOL            | PARAMETER                                                                      | -    | -7   |      | UNIT |     |

|-------------------|--------------------------------------------------------------------------------|------|------|------|------|-----|

| STWIDOL           | FARAMETER                                                                      | MIN. | MAX. | MIN. | MAX. |     |

| t <sub>PD</sub>   | Input or feedback to non-registered output                                     |      | 7.5  |      | 10   | ns  |

| t <sub>SU</sub>   | Setup time from input, feedback or SP to Clock                                 | 3    |      | 4    |      | ns  |

| tco               | Clock to output                                                                |      | 6.75 |      | 8    | ns  |

| t <sub>CF</sub>   | Clock to feedback <sup>1</sup>                                                 |      | 2    |      | 3    | ns  |

| t <sub>H</sub>    | Hold time                                                                      |      | 0    |      | 0    | ns  |

| t <sub>AR</sub>   | Asynchronous Reset to registered output                                        |      | 15   |      | 15   | ns  |

| t <sub>ARW</sub>  | Asynchronous Reset width                                                       | 5    |      | 5    |      | ns  |

| t <sub>ARR</sub>  | Asynchronous Reset recovery time                                               |      | 5    |      | 5    | ns  |

| t <sub>SPR</sub>  | Synchronous Preset recovery time                                               |      | 5    |      | 5    | ns  |

| t <sub>W</sub> ∟  | Width of Clock LOW                                                             | 3    |      | 3    |      | ns  |

| t <sub>WH</sub>   | Width of Clock HIGH                                                            | 3    |      | 3    |      | ns  |

| t <sub>R</sub>    | Input rise time                                                                |      | 20   |      | 20   | ns  |

| t <sub>F</sub>    | Input fall time                                                                |      | 20   |      | 20   | ns  |

| f <sub>MAX1</sub> | Maximum internal frequency <sup>2</sup> 1/(t <sub>SU</sub> + t <sub>CF</sub> ) | 200  |      | 143  |      | MHz |

| f <sub>MAX2</sub> | Maximum external frequency <sup>1</sup> 1/(t <sub>SU</sub> + t <sub>CO</sub> ) | 103  |      | 83   |      | MHz |

| f <sub>MAX3</sub> | Maximum clock frequency <sup>1</sup> 1/(t <sub>WL</sub> + t <sub>WH</sub> )    | 167  |      | 167  |      | MHz |

| t <sub>EA</sub>   | Input to Output Enable                                                         |      | 9    |      | 10   | ns  |

| t <sub>ER</sub>   | Input to Output Disable                                                        |      | 9    |      | 10   | ns  |

| Capacitan         | ce                                                                             | •    | -    | -    | •    | -   |

| C <sub>IN</sub>   | Input pin capacitance                                                          |      | 10   |      | 10   | pF  |

| C <sub>OUT</sub>  | Output capacitance                                                             |      | 12   |      | 12   | pF  |

### NOTES:

These parameters measured with a 10-bit up counter, with all outputs enabled and unloaded. Inputs are tied to V<sub>DD</sub> or ground. These

parameters are not 100% tested, but are calculated at initial characterization and at any time the design is modified where current may be

affected.

<sup>1.</sup> These parameters are not 100% tested, but are calculated at initial characterization and at any time the design is modified where frequency may be affected.

<sup>2.</sup> These parameters measured with a 10-bit up counter, with all outputs enabled and unloaded. Inputs are tied to V<sub>DD</sub> or ground. These parameters are not 100% tested, but are calculated at initial characterization and at any time the design is modified where frequency may be affected.

# 5V zero power, TotalCMOS™, universal PLD device

P5Z22V10

### DC ELECTRICAL CHARACTERISTICS FOR INDUSTRIAL GRADE DEVICES

Industrial: -40°C  $\leq T_{amb} \leq +85$ °C;  $4.5 \leq V_{DD} \leq 5.5V$

| SYMBOL             | PARAMETER                       | TEST CONDITIONS                                         |      | LIMITS |      | UNITS |

|--------------------|---------------------------------|---------------------------------------------------------|------|--------|------|-------|

| STIVIDOL           | PARAMETER                       | TEST CONDITIONS                                         | MIN. | TYP.   | MAX. | UNITS |

| V <sub>IL</sub>    | Input voltage low               | V <sub>DD</sub> = 4.5V                                  |      |        | 0.8  | V     |

| V <sub>IH</sub>    | Input voltage high              | V <sub>DD</sub> = 5.5V                                  | 2    |        |      | V     |

| VI                 | Input clamp voltage             | $V_{DD} = 4.5V; I_{IN} = -18mA$                         |      |        | -1.2 | V     |

| V <sub>OL</sub>    | Output voltage low              | $V_{DD} = 4.5V; I_{OL} = 8mA$                           |      |        | 0.5  | V     |

| V <sub>OH</sub>    | Output voltage high             | $V_{DD} = 4.5V; I_{OL} = -4mA$                          | 2.4  |        |      | V     |

| lı                 | Input leakage current           | $V_{IN} = 0$ to $V_{DD}$                                | -10  |        | 10   | μΑ    |

| loz                | 3-Stated output leakage current | $V_{IN} = 0$ to $V_{DD}$                                | -10  |        | 10   | μΑ    |

| $I_{DDQ}$          | Standby current                 | V <sub>DD</sub> = 5.5V; T <sub>amb</sub> = -40°C        |      | 70     | 95   | μΑ    |

| I <sub>DDD</sub> 1 | Dynamic current                 | V <sub>DD</sub> = 5.5V; T <sub>amb</sub> = -40°C @ 1MHz |      | 1      | 3    | mA    |

| 'ססס               | Dynamic current                 | $V_{DD} = 5.5V$ ; $T_{amb} = -40^{\circ}C$ @ 50MHz      |      | 10     | 20   | mA    |

| I <sub>SC</sub>    | Short circuit output current    | 1 pin/time for no longer than 1 second                  | -30  |        | -100 | mA    |

| C <sub>IN</sub>    | Input pin capacitance           | T <sub>amb</sub> = 25°C; f = 1MHz                       |      |        | 10   | pF    |

| C <sub>CLK</sub>   | Clock input capacitance         | T <sub>amb</sub> = 25°C; f = 1MHz                       | 5    |        | 12   | pF    |

| C <sub>I/O</sub>   | I/O pin capacitance             | T <sub>amb</sub> = 25°C; f = 1MHz                       |      |        | 10   | pF    |

### NOTE:

### AC ELECTRICAL CHARACTERISTICS FOR INDUSTRIAL GRADE DEVICES

Industrial: -40°C  $\leq T_{amb} \leq +85$ °C;  $4.5 \leq V_{DD} \leq 5.5V$

| SYMBOL            | PARAMETER                                                                      | LIF  | LIMITS |      |  |  |

|-------------------|--------------------------------------------------------------------------------|------|--------|------|--|--|

| STIVIDOL          | PANAMETER                                                                      | MIN. | MAX.   | UNIT |  |  |

| t <sub>PD</sub>   | Input or feedback to non-registered output                                     |      | 10     | ns   |  |  |

| t <sub>SU</sub>   | Setup time from input, feedback or SP to Clock                                 | 5    |        | ns   |  |  |

| t <sub>CO</sub>   | Clock to output                                                                |      | 8.5    | ns   |  |  |

| t <sub>CF</sub>   | Clock to feedback <sup>1</sup>                                                 |      | 4      | ns   |  |  |

| t <sub>H</sub>    | Hold time                                                                      |      | 0      | ns   |  |  |

| t <sub>AR</sub>   | Asynchronous Reset to registered output                                        |      | 15     | ns   |  |  |

| t <sub>ARW</sub>  | Asynchronous Reset width                                                       | 5    |        | ns   |  |  |

| t <sub>ARR</sub>  | Asynchronous Reset recovery time                                               |      | 5      | ns   |  |  |

| t <sub>SPR</sub>  | Synchronous Preset recovery time                                               |      | 5      | ns   |  |  |

| t <sub>W</sub> ∟  | Width of Clock LOW                                                             | 3    |        | ns   |  |  |

| t <sub>WH</sub>   | Width of Clock HIGH                                                            | 3    |        | ns   |  |  |

| t <sub>R</sub>    | Input rise time                                                                |      | 20     | ns   |  |  |

| t <sub>F</sub>    | Input fall time                                                                |      | 20     | ns   |  |  |

| f <sub>MAX1</sub> | Maximum internal frequency <sup>2</sup> 1/(t <sub>SU</sub> + t <sub>CF</sub> ) | 111  |        | MHz  |  |  |

| f <sub>MAX2</sub> | Maximum external frequency <sup>1</sup> 1/(t <sub>SU</sub> + t <sub>CO</sub> ) | 74   |        | MHz  |  |  |

| f <sub>MAX3</sub> | Maximum clock frequency <sup>1</sup> 1/(t <sub>WL</sub> + t <sub>WH</sub> )    | 167  |        | MHz  |  |  |

| $t_{EA}$          | Input to Output Enable                                                         |      | 11     | ns   |  |  |

| t <sub>ER</sub>   | Input to Output Disable                                                        |      | 11     | ns   |  |  |

| Capacitan         | ce                                                                             | •    | •      |      |  |  |

| C <sub>IN</sub>   | Input pin capacitance                                                          |      | 10     | pF   |  |  |

| C <sub>OUT</sub>  | Output capacitance                                                             |      | 12     | pF   |  |  |

# NOTES:

These parameters measured with a 10-bit up counter, with all outputs enabled and unloaded. Inputs are tied to V<sub>DD</sub> or ground. These

parameters are not 100% tested, but are calculated at initial characterization and at any time the design is modified where current may be

affected.

These parameters are not 100% tested, but are calculated at initial characterization and at any time the design is modified where frequency

may be affected.

<sup>2.</sup> These parameters measured with a 10-bit up counter, with all outputs enabled and unloaded. Inputs are tied to V<sub>DD</sub> or ground. These parameters are not 100% tested, but are calculated at initial characterization and at any time the design is modified where frequency may be affected.

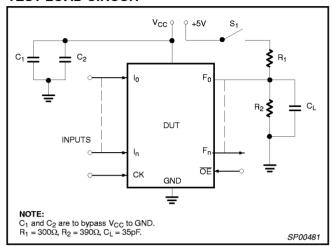

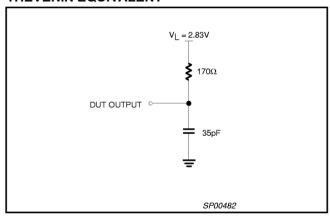

# **TEST LOAD CIRCUIT**

# THEVENIN EQUIVALENT

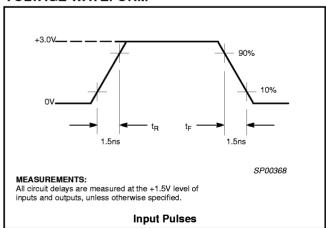

# **VOLTAGE WAVEFORM**

P5Z22V10

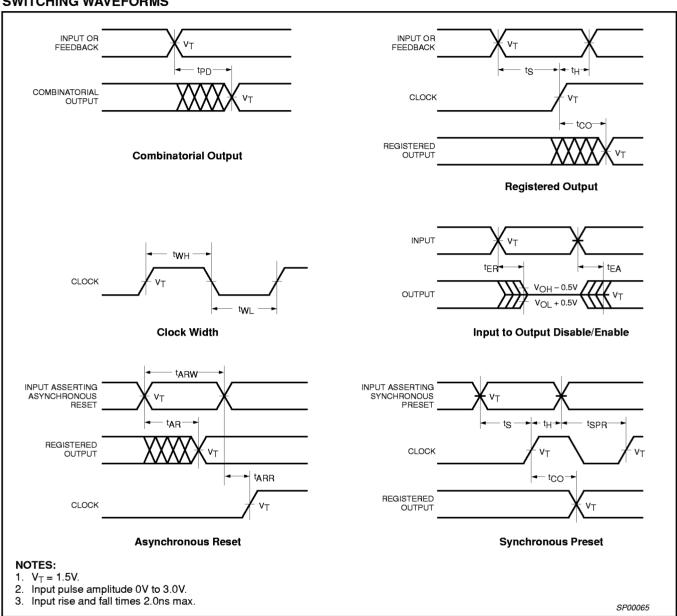

### **SWITCHING WAVEFORMS**

# "AND" ARRAY - (I, B)

# NOTE:

1. This is the initial state.

P5Z22V10

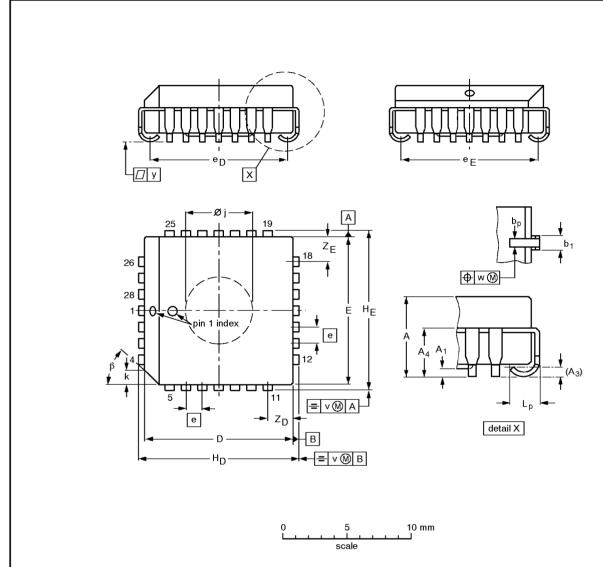

# PLCC28: plastic leaded chip carrer; 28 leads; pedestal

SOT261-3

### DIMENSIONS (millimetre dimensions are derived from the original inch dimensions)

| UNIT   | Α              | A <sub>1</sub><br>min. | <b>A</b> <sub>3</sub> | A <sub>4</sub><br>max. | bp             | b <sub>1</sub> | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>D</sub> | eE             | H <sub>D</sub> | HE             | k              | øj             | Lp             | v     | w     | у     | Z <sub>D</sub> <sup>(1)</sup><br>max. | Z <sub>E</sub> <sup>(1)</sup><br>max. | 1 10 1 |

|--------|----------------|------------------------|-----------------------|------------------------|----------------|----------------|------------------|------------------|------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-------|-------|-------|---------------------------------------|---------------------------------------|--------|

| mm     | 4.57<br>4.19   | 0.13                   | 0.25                  | 3.05                   | 0.53<br>0.33   |                | 11.58<br>11.43   |                  |      | 10.92<br>9.91  | 10.92<br>9.91  |                | 12.57<br>12.32 |                | 5.69<br>5.54   | 1.44<br>1.02   | 0.18  | 0.18  | 0.10  | 2.06                                  | 2.06                                  | 450    |

| inches | 0.180<br>0.165 | 0.005                  | 0.01                  | 0.12                   | 0.021<br>0.013 | 0.032<br>0.026 | 0.456<br>0.450   | 0.456<br>0.450   | 0.05 | 0.430<br>0.390 | 0.430<br>0.390 | 0.495<br>0.485 | 0.495<br>0.485 | 0.048<br>0.042 | 0.224<br>0.218 | 0.057<br>0.040 | 0.007 | 0.007 | 0.004 | 0.081                                 | 0.081                                 | '      |

#### Note

1. Plastic or metal protrusions of 0.01 inches maximum per side are not included.

| OUTLINE  |     | REFER    | EUROPEAN | ISSUE DATE |                                 |

|----------|-----|----------|----------|------------|---------------------------------|

| VERSION  | IEC | JEDEC    | EIAJ     | PROJECTION | ISSUE DATE                      |

| SOT261-3 |     | MO-047AB |          |            | <del>92 11 17</del><br>95-02-25 |

P5Z22V10

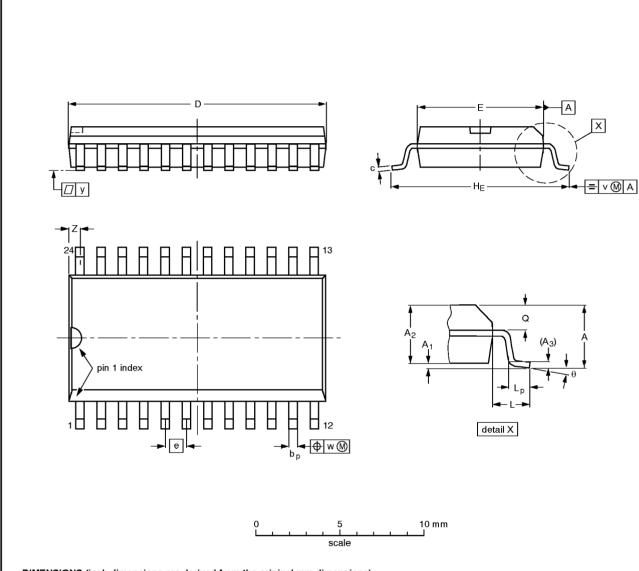

# SO24: plastic small outline package; 24 leads; body width 7.5 mm

SOT137-1

# DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | А3   | bp             | O              | D <sup>(1)</sup> | E <sup>(1)</sup> | е     | HE             | ٦     | Lp                      | ø              | >    | w    | у     | z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|------|----------------|----------------|------------------|------------------|-------|----------------|-------|-------------------------|----------------|------|------|-------|------------------|----|

| mm     | 2.65      | 0.30<br>0.10   | 2.45<br>2.25   | 0.25 | 0.49<br>0.36   | 0.32<br>0.23   | 15.6<br>15.2     | 7.6<br>7.4       | 1.27  | 10.65<br>10.00 | 1.4   | 1.1<br>0.4              | 1.1<br>1.0     | 0.25 | 0.25 | 0.1   | 0.9<br>0.4       | 8° |

| inches | 0.10      | 0.012<br>0.004 | 0.096<br>0.089 | 0.01 | 0.019<br>0.014 | 0.013<br>0.009 | 0.61<br>0.60     | 0.30<br>0.29     | 0.050 | 0.42<br>0.39   | 0.055 | 0.043<br>0.0 <b>1</b> 6 | 0.043<br>0.039 | 0.01 | 0.01 | 0.004 | 0.035<br>0.016   | o° |

#### Note

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

| OUTLINE  |        | REFER    | RENCES | EUROPEAN   | ISSUE DATE                       |  |

|----------|--------|----------|--------|------------|----------------------------------|--|

| VERSION  | IEC    | JEDEC    | EIAJ   | PROJECTION | ISSUE DATE                       |  |

| SOT137-1 | 075E05 | MS-013AD |        |            | <del>-92 11 17</del><br>95-01-24 |  |

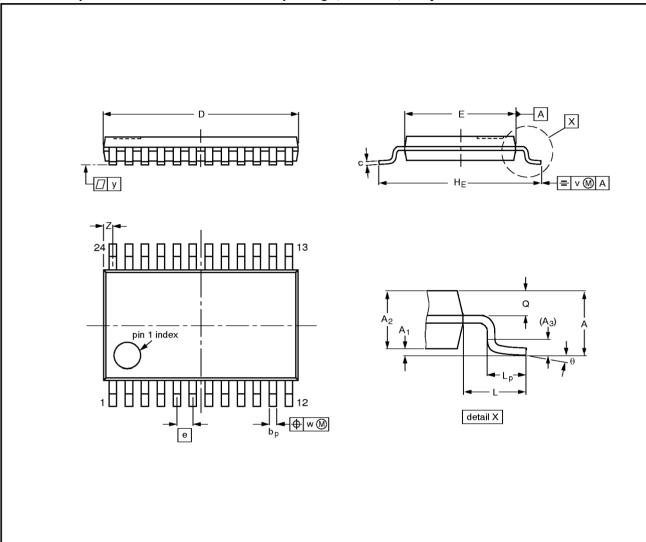

P5Z22V10

TSSOP24: plastic thin shrink small outline package; 24 leads; body width 4.4 mm

SOT355-1

### DIMENSIONS (mm are the original dimensions)

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | Аз   | bр           | С          | D <sup>(1)</sup> | E <sup>(2)</sup> | е    | HE         | L   | Lp           | Q          | v   | w    | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|------|--------------|------------|------------------|------------------|------|------------|-----|--------------|------------|-----|------|-----|------------------|----------|

| mm   | 1.10      | 0.15<br>0.05   | 0.95<br>0.80   | 0.25 | 0.30<br>0.19 | 0.2<br>0.1 | 7.9<br>7.7       | 4.5<br>4.3       | 0.65 | 6.6<br>6.2 | 1.0 | 0.75<br>0.50 | 0.4<br>0.3 | 0.2 | 0.13 | 0.1 | 0.5<br>0.2       | 8°<br>0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER    | RENCES | EUROPEAN   | ISSUE DATE                        |

|----------|-----|----------|--------|------------|-----------------------------------|

| VERSION  | IEC | JEDEC    | EIAJ   | PROJECTION | ISSUEDATE                         |

| SOT355-1 |     | MO-153AD |        |            | <del>-93-06-16-</del><br>95-02-04 |

# 5V zero power, TotalCMOS™, universal PLD device

P5722V10

### Data sheet status

| Data sheet status         | Product<br>status | Definition [1]                                                                                                                                                                                                                                            |

|---------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | Development       | This data sheet contains the design target or goal specifications for product development. Specification may change in any manner without notice.                                                                                                         |

| Preliminary specification | Qualification     | This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips Semiconductors reserves the right to make chages at any time without notice in order to improve design and supply the best possible product. |

| Product specification     | Production        | This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                      |

<sup>[1]</sup> Please consult the most recently issued datasheet before initiating or completing a design.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

**Limiting values definition** — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

**Life support** — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

**Right to make changes** — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 1998 All rights reserved. Printed in U.S.A.

print code Date of release: 07-98

Document order number:

Let's make things better.

Philips Semiconductors