#### XC1700D Family of Serial Configuration PROMs

November 25, 1997 (Version 1.1)

Product Specification

## **Features**

- Extended family of one-time programmable (OTP) bit-serial read-only memories used for storing the configuration bitstreams of Xilinx FPGAs

- On-chip address counter, incremented by each rising edge on the clock input

- Simple interface to the FPGA requires only one user I/O pin

- Cascadable for storing longer or multiple bitstreams

- Programmable reset polarity (active High or active Low) for compatibility with different FPGA solutions

- XC17128D or XC17256D supports XC4000 fast configuration mode (12.5 MHz)

- Low-power CMOS EPROM process

- Available in 5 V and 3.3 V versions

- Available in plastic and ceramic packages, and commercial, industrial and military temperature ranges

- Space efficient 8-pin DIP, 8-pin SOIC, 8-pin VOIC, or 20-pin surface-mount packages.

- Programming support by leading programmer manufacturers.

## Description

The XC1700 family of serial configuration PROMs (SCPs) provides an easy-to-use, cost-effective method for storing Xilinx FPGA configuration bitstreams.

When the FPGA is in master serial mode, it generates a configuration clock that drives the SCP. A short access time after the rising clock edge, data appears on the SCP DATA output pin that is connected to the FPGA DIN pin. The FPGA generates the appropriate number of clock pulses to complete the configuration. Once configured, it disables the SCP. When the FPGA is in slave mode, the SCP and the FPGA must both be clocked by an incoming signal.

Multiple devices can be concatenated by using the  $\overline{CEO}$  output to drive the  $\overline{CE}$  input of the following device. The clock inputs and the DATA outputs of all SCPs in this chain are interconnected. All devices are compatible and can be cascaded with other members of the family.

For device programming, the XACT development system compiles the FPGA design file into a standard Hex format, which is then transferred to the programmer.

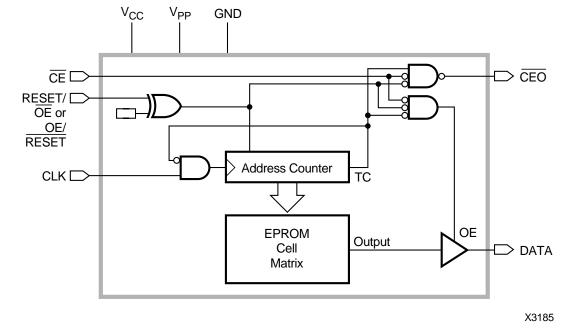

Figure 1: Simplified Block Diagram (does not show programming circuit)

## **Pin Description**

#### DATA

Data output, 3-stated when either  $\overline{CE}$  or  $\overline{OE}$  are inactive. During programming, the DATA pin is I/O. Note that  $\overline{OE}$  can be programmed to be either active High or active Low.

#### CLK

Each rising edge on the CLK input increments the internal address counter, if both  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  are active.

#### RESET/OE

When High, this input holds the address counter reset and 3-states the DATA output. The polarity of this input pin is programmable as either RESET/OE or OE/RESET. To avoid confusion, this document describes the pin as RESET/OE, although the opposite polarity is possible on all devices. When RESET is active, the address counter is held at zero, and the DATA output is 3-stated. The polarity of this input is programmable. The default is active High RESET, but the preferred option is active Low RESET, because it can be driven by the FPGA's INIT pin.

The polarity of this pin is controlled in the programmer interface. This input pin is easily inverted using the Xilinx HW-130 programmer software. Third-party programmers have different methods to invert this pin.

#### CE

When High, this pin disables the internal address counter, 3-states the DATA output, and forces the device into  ${\rm low-I}_{\rm CC}$  standby mode.

#### CEO

Chip Enable output, to be connected to the  $\overline{CE}$  input of the next SCP in the daisy chain. This output is Low when the  $\overline{CE}$  and  $\overline{OE}$  inputs are both active AND the internal address counter has been incremented beyond its Terminal Count (TC) value. In other words: when the PROM has been read,  $\overline{CEO}$  will follow  $\overline{CE}$  as long as  $\overline{OE}$  is active. When  $\overline{OE}$  goes inactive,  $\overline{CEO}$  stays High until the PROM is reset. Note that  $\overline{OE}$  can be programmed to be either active High or active Low.

#### V<sub>PP</sub>

Programming voltage. No overshoot above the specified max voltage is permitted on this pin. For normal read operation, this pin *must* be connected to  $V_{CC}$ . Failure to do so may lead to unpredictable, temperature-dependent operation and severe problems in circuit debugging. *Do not leave VPP floating!*

#### V<sub>CC</sub> and GND

$V_{\mbox{\scriptsize CC}}$  is positive supply pin and GND is ground pin.

#### **Serial PROM Pinouts**

| Pin Name            | 8-Pin | 20-Pin |

|---------------------|-------|--------|

| DATA                | 1     | 2      |

| CLK                 | 2     | 4      |

| RESET/OE (OE/RESET) | 3     | 6      |

| CE                  | 4     | 8      |

| GND                 | 5     | 10     |

| CEO                 | 6     | 14     |

| V <sub>PP</sub>     | 7     | 17     |

| V <sub>CC</sub>     | 8     | 20     |

#### Capacity

| Device                         | Configuration Bits |

|--------------------------------|--------------------|

| XC1718D or L                   | 18,144             |

| XC1736D                        | 36,288             |

| XC1765D or L                   | 65,536             |

| XC17128D or L<br>XC17256D or L | 131,072<br>262,144 |

| XC17512L                       | 524,288            |

| XC1701 or L                    | 1,048,576          |

#### Number of Configuration Bits, Including Header for all Xilinx FPGAs and Compatible SCP Type

| XC3x20A/L   | 44.040    |                       |

|-------------|-----------|-----------------------|

| NO3XZON L   | 14,819    | XC1718D               |

| XC3x30A/L   | 22,216    | XC1736D               |

| XC3x42A/L   | 30,824    | XC1736D               |

| XC3x64A/L   | 46,104    | XC1765D               |

| XC3x90A/L   | 64,200    | XC1765D               |

| XC3195A     | 94,984    | XC17128D              |

| XC4003E     | 53,984    | XC1765D               |

| XC4005E     | 95,008    | XC17128D/L            |

| XC4006E     | 119,840   | XC17128D              |

| XC4008E     | 147,552   | XC17256D              |

| XC4010E     | 178,144   | XC17256D/L            |

| XC4013E     | 247,968   | XC17256D/L            |

| XC4020E     | 329,312   | XC1701                |

| XC4025E     | 422,176   | XC1701                |

| XC4005XL    | 151,960   | XC17256L              |

| XC4010XL    | 283,424   | XC17512L              |

| XC4013XL    | 393,623   | XC17512L              |

| XC4020XL    | 521,880   | XC17512L              |

| XC4028EX/XL | 668,184   | XC1701L               |

| XC4036EX/XL | 832,528   | XC1701L               |

| XC4044XL    | 1,014,928 | XC1701L               |

| XC4052XL    | 1,215,368 | XC1701L +<br>XC17256L |

| XC4062XL    | 1,433,864 | XC1701L +<br>XC17512L |

| XC4085XL    | 1,924,992 | 2 XC1701L             |

| XC5202      | 42,416    | XC1765D               |

| XC5204      | 70,704    | XC17128D              |

| XC5206      | 106,288   | XC17128D              |

| XC5210      | 165,488   | XC17256D              |

| XC5215      | 237,744   | XC17256D              |

# **Controlling Serial PROMs**

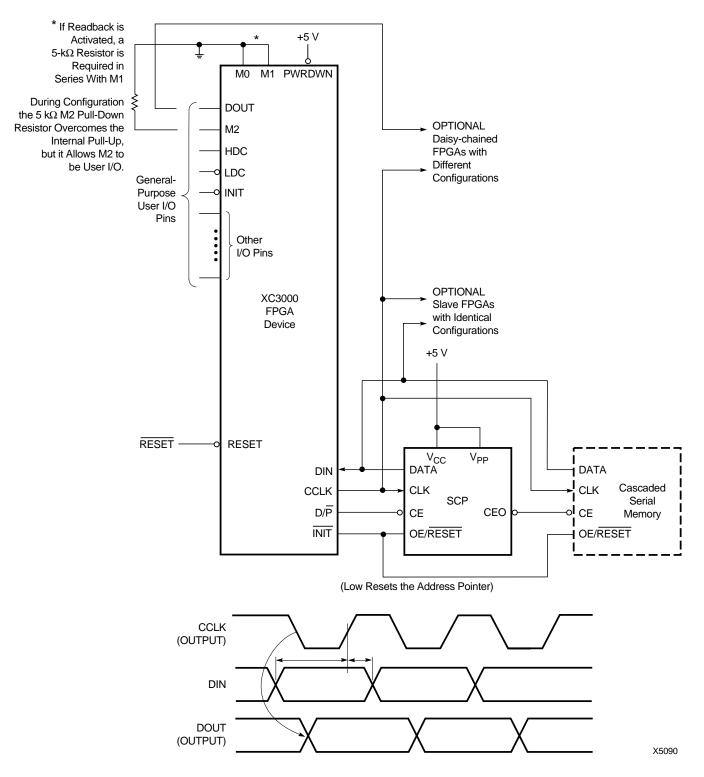

Most connections between the FPGA device and the Serial PROM are simple and self-explanatory.

- The DATA output(s) of the of the Serial PROM(s) drives the DIN input of the lead FPGA device.

- The master FPGA CCLK output drives the CLK input(s) of the Serial PROM(s).

- The CEO output of a Serial PROM drives the CE input of the next Serial PROM in a daisy chain (if any).

- The RESET/OE input of all Serial PROMs is best driven by the INIT output of the XC3000 or XC4000 lead FPGA device. This connection assures that the Serial PROM address counter is reset before the start of any (re)configuration, even when a reconfiguration is initiated by a V<sub>CC</sub> glitch. Other methods – such as driving RESET/OE from LDC or system reset – assume that the Serial PROM internal power-on-reset is always

in step with the FPGA's internal power-on-reset, which may not be a safe assumption.

The CE input of the lead (or only) Serial PROM is driven by the DONE/PRGM or DONE output of the lead FPGA device, provided that DONE/PRGM is not permanently grounded. Otherwise, LDC can be used to drive CE, but must then be unconditionally High during user operation. CE can also be permanently tied Low, but this keeps the DATA output active and causes an unnecessary supply current of 10 mA maximum.

## FPGA Master Serial Mode Summary

The I/O and logic functions of the Logic Cell Array and their associated interconnections are established by a configuration program. The program is loaded either automatically upon power up, or on command, depending on the state of the three FPGA mode pins. In Master Mode, the FPGA automatically loads the configuration program from an external memory. The Serial Configuration PROM has been designed for compatibility with the Master Serial Mode.

Upon power-up or reconfiguration, an FPGA enters the Master Serial Mode whenever all three of the FPGA modeselect pins are Low (M0=0, M1=0, M2=0). Data is read from the Serial Configuration PROM sequentially on a single data line. Synchronization is provided by the rising edge of the temporary signal CCLK, which is generated during configuration.

Master Serial Mode provides a simple configuration interface. Only a serial data line and two control lines are required to configure an FPGA. Data from the Serial Configuration PROM is read sequentially, accessed via the internal address and bit counters which are incremented on every valid rising edge of CCLK.

If the user-programmable, dual-function DIN pin on the FPGA is used only for configuration, it must still be held at a defined level during normal operation. The XC3000 and XC4000 families take care of this automatically with an onchip default pull-up resistor. With XC2000-family devices, the user must either configure DIN as an active output, or provide a defined level, e.g., by using an external pull-up resistor, if DIN is configured as an input.

#### Programming the FPGA With Counters Unchanged Upon Completion

When multiple FPGA-configurations for a single FPGA are stored in a Serial Configuration PROM, the  $\overline{OE}$  pin should be tied Low. Upon power-up, the internal address counters are reset and configuration begins with the first program stored in memory. Since the  $\overline{OE}$  pin is held Low, the address counters are left unchanged after configuration is complete. Therefore, to reprogram the FPGA with another program, the D/P line is pulled Low and configuration begins at the last value of the address counters.

This method fails if a user applies RESET during the FPGA configuration process. The FPGA aborts the configuration and then restarts a new configuration, as intended, but the Serial PROM does not reset its address counter, since it never saw a High level on its  $\overline{OE}$  input. The new configuration, therefore, reads the remaining data in the PROM and interprets it as preamble, length count etc. Since the FPGA is the master, it issues the necessary number of CCLK pulses, up to 16 million (2<sup>24</sup>) and D/P goes High. However, the FPGA configuration will be completely wrong, with potential contentions inside the FPGA and on its output pins. This method must, therefore, never be used when there is any chance of external reset during configuration.

#### **Cascading Serial Configuration PROMs**

For multiple FPGAs configured as a daisy-chain, or for future FPGAs requiring larger configuration memories, cas-

caded SCPs provide additional memory. After the last bit from the first SCP is read, the next clock signal to the SCP asserts its  $\overline{CEO}$  output Low and disables its DATA line. The second SCP recognizes the Low level on its  $\overline{CE}$  input and enables its DATA output. See Figure 2.

After configuration is complete, the address counters of all cascaded SCPs are reset if the FPGA  $\overline{\text{RESET}}$  pin goes Low, assuming the SCP reset polarity option has been inverted.

To reprogram the FPGA with another program, the  $D/\overline{P}$  line goes Low and configuration begins where the address counters had stopped. In this case, avoid contention between DATA and the configured I/O use of DIN.

**Figure 2:** Master Serial Mode. The one-time-programmable Serial Configuration PROM supports automatic loading of configuration programs. Multiple devices can be cascaded to support additional FPGA. An early D/P inhibits the PROM data output one CCLK cycle before the FPGA I/Os become active.

#### **Standby Mode**

The PROM enters a low-power standby mode whenever  $\overline{CE}$  is asserted High. The output remains in a high impedance state regardless of the state of the  $\overline{OE}$  input.

# Programming the XC1700 Family Serial PROMs

The devices can be programmed on programmers supplied by Xilinx or qualified third-party vendors. The user must ensure that the appropriate programming algorithm and the latest version of the programmer software are used. The wrong choice can permanently damage the device.

| Control I | nputs | Internal Address                                                      | Outputs           |             |                   |  |

|-----------|-------|-----------------------------------------------------------------------|-------------------|-------------|-------------------|--|

| RESET     | CE    |                                                                       | DATA              | CEO         | I <sub>cc</sub>   |  |

| Inactive  | Low   | if address <u>&lt;</u> TC: increment<br>if address > TC: don't change | active<br>3-state | High<br>Low | active<br>reduced |  |

| Active    | Low   | Held reset                                                            | 3-state           | High        | active            |  |

| Inactive  | High  | Not changing                                                          | 3-state           | High        | standby           |  |

| Active    | High  | Held reset                                                            | 3-state           | High        | standby           |  |

#### Table 1: Truth Table for XC1700 Control Inputs

**Notes:** 1. The XC1700 RESET input has programmable polarity

2. TC = Terminal Count = highest address value. TC+1 = address 0.

## XC1718D, XC1736D, XC1765D, XC17128D and XC17256D

### **Absolute Maximum Ratings**

| Symbol           | Description                                     |                              | Units |

|------------------|-------------------------------------------------|------------------------------|-------|

| V <sub>CC</sub>  | Supply voltage relative to GND                  | -0.5 to +7.0                 | V     |

| V <sub>PP</sub>  | Supply voltage relative to GND                  | -0.5 to +12.5                | V     |

| V <sub>IN</sub>  | Input voltage relative to GND                   | -0.5 to V <sub>CC</sub> +0.5 | V     |

| V <sub>TS</sub>  | Voltage applied to 3-state output               | -0.5 to V <sub>CC</sub> +0.5 | V     |

| T <sub>STG</sub> | Storage temperature (ambient)                   | -65 to +150                  | °C    |

| T <sub>SOL</sub> | Maximum soldering temperature (10 s @ 1/16 in.) | +260                         | °C    |

Note: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

### **Operating Conditions**

| Symbol          | Description |                                                        | Min  | Мах  | Units |

|-----------------|-------------|--------------------------------------------------------|------|------|-------|

| V <sub>CC</sub> | Commercial  | Supply voltage relative to GND 0°C to +70°C junction   | 4.75 | 5.25 | V     |

|                 | Industrial  | Supply voltage relative to GND -40°C to +85°C junction | 4.50 | 5.50 | V     |

|                 | Military    | Supply voltage relative to GND -55°C to +125°C case    | 4.50 | 5.50 | V     |

## **DC Characteristics Over Operating Condition**

| Symbol           | Description                                         |                                                  | Min   | Max  | Units |  |

|------------------|-----------------------------------------------------|--------------------------------------------------|-------|------|-------|--|

| V <sub>IH</sub>  | High-level input voltage                            |                                                  |       |      |       |  |

| V <sub>IL</sub>  | Low-level input voltage                             | •<br>•                                           |       |      |       |  |

| V <sub>OH</sub>  | High-level output voltage (I <sub>OH</sub> = -4 mA) | Commercial                                       | 3.86  |      | V     |  |

| V <sub>OL</sub>  | Low-level output voltage (I <sub>OL</sub> = +4 mA)  |                                                  |       | 0.32 | V     |  |

| V <sub>OH</sub>  | High-level output voltage (I <sub>OH</sub> = -4 mA) | Industrial                                       | 3.76  |      | V     |  |

| V <sub>OL</sub>  | Low-level output voltage (I <sub>OL</sub> = +4 mA)  |                                                  |       | 0.37 | V     |  |

| V <sub>OH</sub>  | High-level output voltage (I <sub>OH</sub> = -4 mA) | Military                                         | 3.7   |      | V     |  |

| V <sub>OL</sub>  | Low-level output voltage (I <sub>OL</sub> = +4 mA)  |                                                  |       | 0.4  | V     |  |

| I <sub>CCA</sub> | Supply current, active mode                         |                                                  |       | 10.0 | mA    |  |

| I <sub>CCS</sub> | Supply current, standby mode, XC17128D, XC17256     | Supply current, standby mode, XC17128D, XC17256D |       |      |       |  |

|                  | Supply current, standby mode, XC1718D, XC1736D,     | XC1765D                                          |       | 1.5  | mA    |  |

| IL.              | Input or output leakage current                     |                                                  | -10.0 | 10.0 | μΑ    |  |

Note: During normal read operation  $V_{PP}$  must be connected to  $V_{CC}$

## XC1718L, XC1765L, XC17128L and XC17256L

## Absolute Maximum Ratings

| Symbol           | Description                                     |                              | Units |

|------------------|-------------------------------------------------|------------------------------|-------|

| V <sub>CC</sub>  | Supply voltage relative to GND                  | -0.5 to +6.0                 | V     |

| V <sub>PP</sub>  | Supply voltage relative to GND                  | -0.5 to +12.5                | V     |

| V <sub>IN</sub>  | Input voltage with respect to GND               | -0.5 to V <sub>CC</sub> +0.5 | V     |

| V <sub>TS</sub>  | Voltage applied to 3-state output               | -0.5 to V <sub>CC</sub> +0.5 | V     |

| T <sub>STG</sub> | Storage temperature (ambient)                   | -65 to +150                  | °C    |

| T <sub>SOL</sub> | Maximum soldering temperature (10 s @ 1/16 in.) | +260                         | °C    |

**Note:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

## **Operating Conditions**

| Symbol          | Description |                                                      | Min | Мах | Units |

|-----------------|-------------|------------------------------------------------------|-----|-----|-------|

| V <sub>CC</sub> | Commercial  | Supply voltage relative to GND 0°C to +70°C junction | 3.0 | 3.6 | V     |

## **DC Characteristics Over Operating Condition**

| Symbol           | Description                                                                                        | Min   | Max             | Units    |

|------------------|----------------------------------------------------------------------------------------------------|-------|-----------------|----------|

| V <sub>IH</sub>  | High-level input voltage                                                                           | 2.0   | V <sub>CC</sub> | V        |

| V <sub>IL</sub>  | Low-level input voltage                                                                            | 0     | 0.8             | V        |

| V <sub>OH</sub>  | High-level output voltage (I <sub>OH</sub> = -4 mA)                                                | 2.4   |                 | V        |

| V <sub>OL</sub>  | Low-level output voltage (I <sub>OL</sub> = +4 mA)                                                 |       | 0.4             | V        |

| I <sub>CCA</sub> | Supply current, active mode                                                                        |       | 5.0             | mA       |

| I <sub>CCS</sub> | Supply current, standby mode, XC1718L, XC1765L<br>Supply current, standby mode, XC17128L, XC17265L |       | 1.5<br>50.0     | mA<br>μA |

| ΙL               | Input or output leakage current                                                                    | -10.0 | 10.0            | μΑ       |

Note: During normal read operation  $V_{PP}$  must be connected to  $V_{CC}$

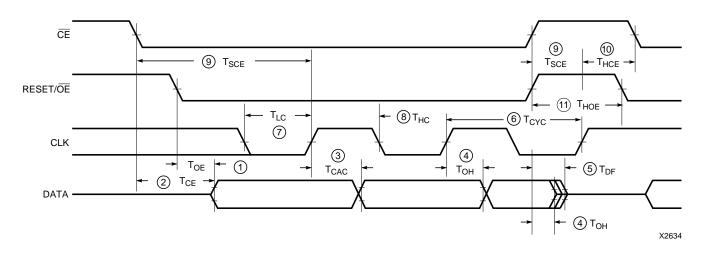

# **AC Characteristics Over Operating Condition**

| Symbol |                  | Description                                               |     | XC1736D |     | XC1718L<br>XC1765L |     | XC17128D<br>XC17256D |     | XC17128L<br>XC17256L |    |

|--------|------------------|-----------------------------------------------------------|-----|---------|-----|--------------------|-----|----------------------|-----|----------------------|----|

|        |                  |                                                           | Min | Max     | Min | Max                | Min | Max                  | Min | Max                  |    |

| 1      | T <sub>OE</sub>  | OE to Data Delay                                          |     | 45      |     | 45                 |     | 25                   |     | 30                   | ns |

| 2      | T <sub>CE</sub>  | CE to Data Delay                                          |     | 60      |     | 60                 |     | 45                   |     | 60                   | ns |

| 3      | T <sub>CAC</sub> | CLK to Data Delay                                         |     | 150     |     | 200                |     | 50                   |     | 60                   | ns |

| 4      | Т <sub>ОН</sub>  | Data Hold From $\overline{CE}$ , $\overline{OE}$ , or CLK | 0   |         | 0   |                    | 0   |                      | 0   |                      | ns |

| 5      | T <sub>DF</sub>  | CE or OE to Data Float Delay <sup>2</sup>                 |     | 50      |     | 50                 |     | 50                   |     | 50                   | ns |

| 6      | T <sub>CYC</sub> | Clock Periods                                             | 200 |         | 400 |                    | 80  |                      | 100 |                      | ns |

| 7      | T <sub>LC</sub>  | CLK Low Time <sup>3</sup>                                 | 100 |         | 100 |                    | 20  |                      | 25  |                      | ns |

| 8      | THC              | CLK High Time <sup>3</sup>                                | 100 |         | 100 |                    | 20  |                      | 25  |                      | ns |

| 9      | TSCE             | CE Setup Time to CLK (to guarantee proper counting)       | 25  |         | 40  |                    | 20  |                      | 25  |                      | ns |

| 10     | T <sub>HCE</sub> | CE Hold Time to CLK (to guarantee proper counting)        | 0   |         | 0   |                    | 0   |                      | 0   |                      | ns |

| 11     | T <sub>HOE</sub> | OE Hold Time (guarantees counters are reset)              | 100 |         | 100 |                    | 20  |                      | 25  |                      | ns |

Notes: 1. AC test load = 50 pF

2. Float delays are measured with minimum tester ac load and maximum dc load. 3. Guaranteed by design, not tested. 4. All AC parameters are measured with  $V_{IL} = 0.0 \text{ V}$  and  $V_{IH} = 3.0 \text{ V}$ .

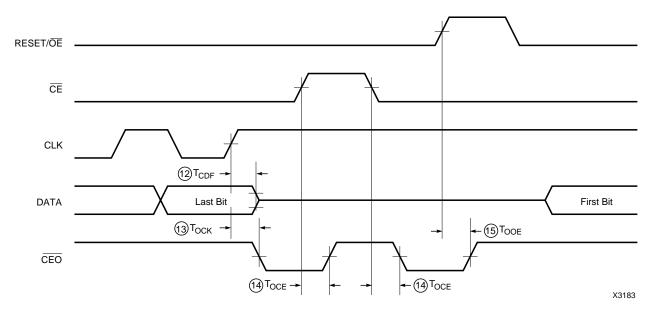

# AC Characteristics Over Operating Condition (continued)

| Symbol |                  | Description                          | XC17<br>XC17<br>XC17 | 736D | XC1<br>XC1 |     | XC17<br>XC17 |     | XC17<br>XC17 |     | Units |

|--------|------------------|--------------------------------------|----------------------|------|------------|-----|--------------|-----|--------------|-----|-------|

|        |                  |                                      | Min                  | Max  | Min        | Max | Min          | Max | Min          | Мах |       |

| 12     | T <sub>CDF</sub> | CLK to Data Float Delay <sup>2</sup> |                      | 50   |            | 50  |              | 50  |              | 50  | ns    |

| 13     | Тоск             | CLK to CEO Delay                     |                      | 65   |            | 65  |              | 30  |              | 30  | ns    |

| 14     | T <sub>OCE</sub> | CE to CEO Delay                      |                      | 45   |            | 45  |              | 35  |              | 35  | ns    |

| 15     | T <sub>OOE</sub> | RESET/OE to CEO Delay                |                      | 40   |            | 40  |              | 30  |              | 30  | ns    |

Notes: 1. AC test load = 50 pF

2. Float delays are measured with minimum tester ac load and maximum dc load.

3. Guaranteed by design, not tested. 4. All AC parameters are measured with V<sub>IL</sub> = 0.0 V and V<sub>IH</sub> = 3.0 V.

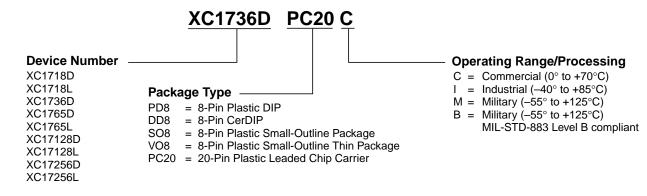

### **Ordering Information**

### **Valid Ordering Combinations**

| XC17128DPD8C  | XC1718DPD8C  | XC17256DPD8C  | XC1736DPD8C  | XC1765DPD8C  |

|---------------|--------------|---------------|--------------|--------------|

| XC17128DVO8C  | XC1718DSO8C  | XC17256DVO8C  | XC1736DSO8C  | XC1765DSO8C  |

| XC17128DPC20C | XC1718DVO8C  | XC17256DPC20C | XC1736DVO8C  | XC1765DVO8C  |

| XC17128DPD8I  | XC1718DPC20C | XC17256DPD8I  | XC1736DPC20C | XC1765DPC20C |

| XC17128DVO8I  | XC1718DPD8I  | XC17256DVO8I  | XC1736DPD8I  | XC1765DPD8I  |

| XC17128DPC20I | XC1718DSO8I  | XC17256DPC20I | XC1736DSO8I  | XC1765DSO8I  |

| XC17128DDD8M  | XC1718DVO8I  | XC17256DDD8M  | XC1736DVO8I  | XC1765DVO8I  |

|               | XC1718DPC20I | XC17256DDD8B  | XC1736DPC20I | XC1765DPC20I |

|               |              |               | XC1736DDD8M  | XC1765DDD8M  |

|               |              |               |              | XC1765DDD8B  |

| XC17128LPD8C  | XC1718LPD8C  | XC17256LPD8C  |              | XC1765LPD8C  |

| XC17128LVO8C  | XC1718LSO8C  | XC17256LVO8C  |              | XC1765LSO8C  |

| XC17128LPC20C | XC1718LVO8C  | XC17256LPC20C |              | XC1765LVO8C  |

| XC17128LPD8I  | XC1718LPC20C | XC17256LPD8I  |              | XC1765LPC20C |

| XC17128LVO8I  | XC1718LPD8I  | XC17256LVO8I  |              | XC1765LPD8I  |

| XC17128LPC20I | XC1718LSO8I  | XC17256LPC20I |              | XC1765LSO8I  |

|               | XC1718LVO8I  |               |              | XC1765LVO8I  |

|               | XC1718LPC20I |               |              | XC1765LPC20I |

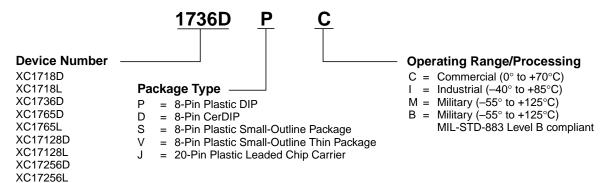

#### **Marking Information**

Due to the small size of the serial PROM package, the complete ordering part number cannot be marked on the package. The XC prefix is deleted and the package code is simplified. Device marking is as follows.