- Programmable Replacement for Conventional TTL, 74HC, and 20-Pin PLD Family

- High-Voltage EPIC™ Process Allows for Higher Performance as Follows: Maximum t<sub>pd</sub>: -12C . . . 12 ns

-15C . . . 15 ns

User-Programmable Output Logic Macrocells Provide Flexibility in Output Types With:

> Selectable for Registered or Combinational Operation Output Polarity Control Independently User Programmable Feedback Path

- Programmable Design-Security Bit Prevents Copying of Logic Stored in Device

- Third-Party Advanced Software Support Featuring Schematic Capture, Interactive Netlist, Boolean Equations, and State-Machine Design Entry

- Package Options Include:

20-pin Plastic Dual-in-Line (N)

20-pin Plastic Chip Carrier (FN)

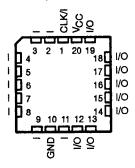

## N PACKAGE (TOP VIEW)

## FN PACKAGE (TOP VIEW)

Pin assignments in operating mode

# description

#### general

The EP330 features advanced-CMOS speed and very low power utilizing Texas Instruments High-Voltage Enhanced-Processed Implanted CMOS (HVEPIC) process. Each output has an Output-Logic-Macrocell (OLM) configuration that allows user definition of the output type. The EP330 provides a reliable low-power substitute for numerous high-performance TTL PLDs.

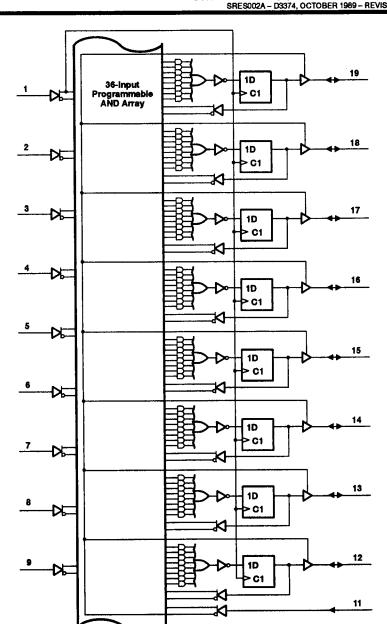

The EP330 can accommodate up to 18 inputs and up to eight outputs. The 20-pin 300-mil package contains eight macrocells each using a programmable AND/fixed-OR structure. This AND-OR structure yields eight product terms for the logic function as well as an individual term for Output Enable.

#### **AVAILABLE OPTIONS**

|                         |                | PACKA                          | GE TYPE                         |

|-------------------------|----------------|--------------------------------|---------------------------------|

| T <sub>A</sub><br>RANGE | 8PEED<br>CLASS | PLASTIC<br>DUAL-IN-LINE<br>(N) | PLASTIC<br>CHIP CARRIER<br>(FN) |

|                         | 12 ns          | EP330-12CN                     | EP330-12CFN                     |

| 0°C to 70°C             | 15 ns          | EP330-15CN                     | EP330-15CFN                     |

| -40°C to 85°C           | 25 ns          | EP330-25IN                     | EP330-25IFN                     |

EPIC is a trademark of Texas Instruments Incorporated.

# EP330 SERIES HIGH-PERFORMANCE 8-MACROCELL ONE-TIME PROGRAMMABLE LOGIC DEVICES

SRES002A - D3374, OCTOBER 1989 - REVISED SEPTEMBER 1992

## description (continued)

The EP330 output-logic macrocell allows the user to configure output and feedback paths for combinational or registered operation either active high or active low. With propagation delays of 12 and 15 ns, the EP330 may be configured as a low-power substitute for popular fast PLD devices such as the PAL16XXB series or the 'PAL16XX-12 and 'PAL16XX-15 series.

The CMOS EPROM technology makes it possible for the EP330 to operate at an active power-consumption level that is less than 75% of equivalent bipolar devices without sacrificing speed performance. This technology also facilitates 100% generic wafer testability using the UV-light erasable capability. As a result, designs and design modification can be quickly effected with a given EP330 without the need for post-programming testing.

Programming the EP330 is made easy by the availability of extensive third-party support for design entry, design processing, and device programming.

The EP330C is characterized for operation from 0°C to 70°C. The EP330I is characterized for operation from -40°C to 85°C.

#### functional description

Externally, the EP330 provides ten dedicated inputs (one of which may be used as a synchronous clock input) and eight I/O pins that may be configured for input, output, or bidirectional operation.

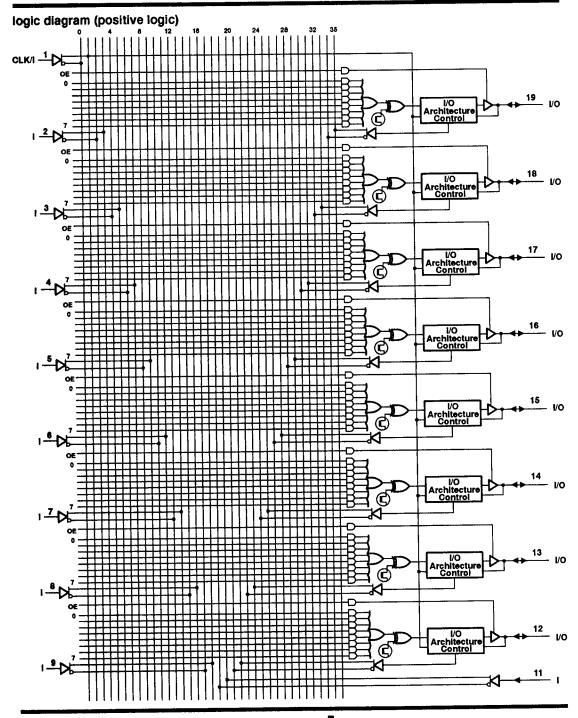

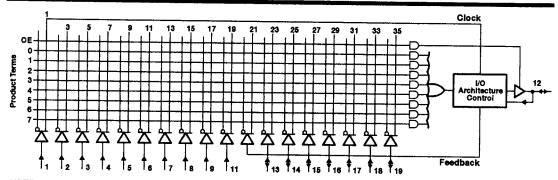

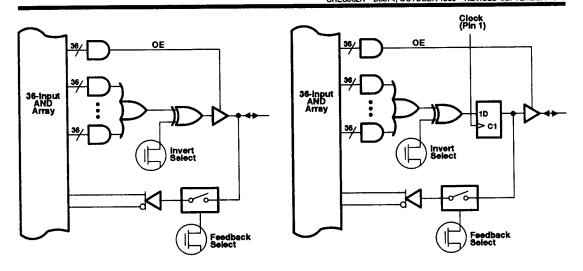

The logic diagram shows the complete EP330, while Figure 1 shows the basic EP330 macrocell. The internal architecture is organized with the familiar sum of products (AND-OR) structure. Inputs to the programmable AND array (shown running vertically in Figure 1) come from two sources: first, the true and complement of the ten dedicated input pins and second, the true and complement of the eight feedback signals, each one originating from an I/O architecture-control block. The 36-input AND array encompasses a total of 72 product terms distributed equally among the eight macrocells. Each product term (shown running horizontally in the logic diagram) represents a 36-input AND gate.

As shown in the logic diagram, the outputs of eight product terms are ORed together, then the output of the OR gate is sent as an input to an exclusive-OR gate. The purpose of this exclusive-OR gate is to allow the user to specify the polarity of the output signal by using the invert-select EPROM cell (active high if the EPROM cell is programmed and active low if it is not programmed).

The exclusive-OR output then feeds the I/O architecture control block. The control block configures the output for registered or combinational operation. In the registered configuration, the output is registered via a positive edge-triggered D-type flip-flop. In this condition, the feedback signal going to the array is also registered and comes directly from the output of the D-type flip-flop. In the combinational configuration, the output is nonregistered and the feedback signal comes directly from the I/O pin. In the erased state, the EP330 contains the same architectural characteristics as the 'PAL16L8.

NOTES: A. This diagram shows one of the eight macrocells within the EP330.

B. The double-arrow lines (‡) show I/O feedback from a macrocell.

Figure 1. Logic Array Macrocell

# output-enable product term

The output enable (OE) product term determines whether an output signal is allowed to propagate to the output pin. If the output of the OE product term is low, then the output buffer becomes a high-impedance node, thus inhibiting the output signal from reaching the output pin. For combinational configurations, this OE product term can be used to allow for true bidirectional operation.

The EP330 contains eight separate OE product terms, one per I/O pin. If it is desired that all outputs be enabled or disabled simultaneously, use an identically programmed product term at each of the outputs. If different outputs are to be enabled under different conditions, different OE product terms for each specific output may be defined.

### I/O architecture

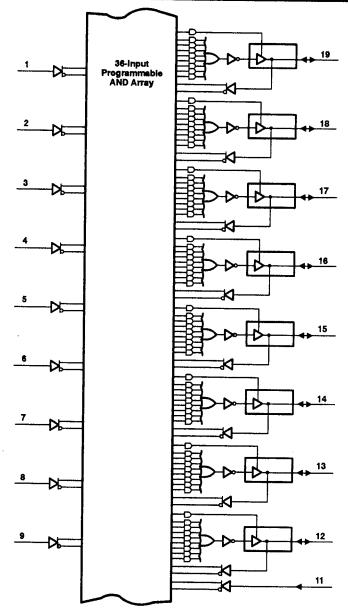

Figure 2 shows the different output configurations that can be chosen for any of the eight I/O pins on the EP330. Because of the individuality of each I/O architecture control block, both registered and combinational output can be chosen on a given EP330 device.

In the combinational configuration, either active-high or active-low output polarity can be chosen. Pin feedback or no feedback is also optional. In the registered configuration, the user has control over output polarity and may choose to use the internal feedback path or no feedback. Any I/O pin can be configured as a dedicated input by choosing no output and no feedback from the array. In the erased state, the I/O architecture is configured for a combinational active-low output with pin feedback.

| OUTPUT/POLARITY    | FEEDBACK  |

|--------------------|-----------|

| Combinational/High | Pin, None |

| Combinational/Low  | Pin, None |

| None               | Pin       |

| OUTPUT/POLARITY | FEEDBACK         |

|-----------------|------------------|

| D Register/High | D Register, None |

| D Register/Low  | D Register, None |

| None            | D Register       |

(a) COMBINATIONAL CONFIGURATION

(b) REGISTERED CONFIGURATION

Figure 2. I/O Configurations

# **PLD** compatibility

Figures 2(a) and 2(b) show how an EP330 can be configured as a drop-in replacement for two commonly used members of the 20-pin PLD family: the 'PAL16L8 and the 'PAL16R8. When configured in these manners, the EP330 is both a functional replacement, as well as a pin-to-pin replacement, for the 'PAL16L8 and 'PAL16R8.

Tables 1 and 2 provide additional information concerning the EP330 as a replacement for the 20-pin PLD family of devices.

- Invert Select EPROM cell is in the erased state providing active-low outputs.

- Combinational Mode is chosen providing Combinational Output with Input (Pin) Feedback.

- 8-product-term OR gate compared to 7-product-term OR gate on 'PAL16L8.

- Pin feedback to the array at 12 through 19 is not available in 'PAL16L8.

Figure 3. EP330 Configuration for Replacing a 'PAL16L8

- Invert Select EPROM cell is in the erased state providing active-low outputs.

- Registered Mode is chosen providing Registered Output with Registered Feedback.

- Complement of pin 11 is used as common OE term for all eight output pins.

Figure 4. EP330 Configuration for Replacing a 'PAL16R8

# **EP330 SERIES** HIGH-PERFORMANCE 8-MACROCELL ONE-TIME PROGRAMMABLE LOGIC DEVICES SRES002A - D3374, OCTOBER 1989 - REVISED SEPTEMBER 1982

Table 1. Configurations for 20-Pin PLD Replacement

| PLD         | EP330      | EP330            | VO                             | OUTPUT/            | T           |

|-------------|------------|------------------|--------------------------------|--------------------|-------------|

| PART NUMBER | PIN NUMBER | MACROCELL NUMBER | CONFIGURATION MODE             | POLARITY           | FEEDBACK    |

| 10H8        | 12-19      | 1-8              | Combinational                  | Comb/High          | None        |

| 10L8        | 12-19      | 1-8              | Combinational                  | Comb/Low           | None        |

|             | 12         | 8                | Combinational                  | None               | Pin         |

| 12HB        | 13-18      | 2-7              | Combinational                  | Comb/High          | None        |

|             | 19         | 1                | Combinational                  | None               | Pin         |

|             | 12         | 8                | Combinational                  | None               | Pin         |

| 12L6        | 13-18      | 2-7              | Combinational                  | Comb/Low           | None        |

|             | 19         | 1 1              | Combinational                  | None               | Pin         |

|             | 12-13      | 7-8              | Combinational                  | None               | Pin         |

| 14H4        | 14-17      | 3-6              | Combinational                  | Comb/High          | None        |

|             | 18-19      | 1-2              | Combinational                  | None               | Pin         |

|             | 12-13      | 7-8              | Combinational                  | None               | Pin         |

| 14L4        | 14-17      | 3-6              | Combinational                  | Comb/Low           | None        |

|             | 18-19      | 1-2              | Combinational                  | None               | Pin         |

|             | 12-14      | 6-8              | Combinational                  | None               | Pin         |

| 4004        | 15         | 5                | Combinational                  | Comb/Low           |             |

| 16C1        | 16         | 4                | Combinational                  | Comb/High          | None        |

|             | 17-19      | 1-3              | Combinational                  | None               | None<br>Pin |

|             | 12-14      | 6-8              | Combinational                  | None               | Pin         |

| 16H2        | 15-16      | 4-5              | Combinational                  |                    | 1           |

|             | 17-19      | 1-3              | Combinational                  | Comb/High          | None        |

|             | 12-14      | 6-8              | Combinational                  | None<br>None       | Pin         |

| 16L2        | 15-16      | 4-5              | Combinational                  | i .                | Pin         |

|             | 17-19      | 1-3              | Combinational                  | Comb/Low           | None        |

| 16H8        | 12         | 8                | Combinational                  | None<br>Comb (None | Pin         |

| 8           | 13-18      | 2-7              | Combinational                  | Comb/High/Z        | None        |

| 16HD8       | 19         | 1                | Combinational                  | Comb/High/Z        | Comb        |

| 16L8        | 12         | 8                | Combinational                  | Comb/High/Z        | None        |

| &           | 13-18      | 2-7              | Combinational                  | Comb/Low/Z         | None        |

| 16LD8       | 19         | 1                | Combinational                  | Comb/Low/Z         | Comb        |

|             | 12-13      | 7-8              | Combinational                  | Comb/Low/Z         | None        |

| 16R4        | 14-17      | 3-8              | Registered                     | Comb/Low/Z         | Comb        |

|             | 18-19      | 1-2              | Combinational                  | Reg/Low/Z          | Reg         |

|             | 12         | 8                | Combinational                  | Comb/Low/Z         | Comb        |

| 16R6        | 13-18      | 2-7              | Registered                     | Comb/Low/Z         | Comb        |

|             | 19         | 1                | Combinational                  | Reg/Low/Z          | Reg         |

| 16R8        | 12-19      | 1-8              | Registered                     | Comb/Low/Z         | Comb        |

|             | 12         | 8                |                                | Reg/Low/Z          | Reg         |

| 16P8        | 13-18      | 2-7              | Combinational<br>Combinational | Comb/Option/Z      | None        |

| -           | 19         | 1                | Combinational Combinational    | Comb/Option/Z      | Comb        |

|             | 12-13      | 7-8              | Combinational                  | Comb/Option/Z      | None        |

| 16RP4       | 14-17      | 3-6              |                                | Comb/Option/Z      | Comb        |

|             | 18-19      | 1-2              | Registered                     | Reg/Option/Z       | Reg         |

|             | 12         | 8                | Combinational                  | Comb/Option/Z      | Comb        |

| 16RP6       | 13-18      | 2-7              | Combinational                  | Comb/Option/Z      | Comb        |

|             | 19         | 1                | Registered                     | Re/Option/Z        | Reg         |

| 16RP8       | 12-19      | 1-8              | Combinational                  | Comb/Option/Z      | Comb        |

|             | 14-19      | <u>I*0</u>       | Registered                     | Reg/Option/Z       | Reg         |

SRES002A - D3374, OCTOBER 1989 - REVISED SEPTEMBER 1992

# Table 2. Device Specifications<sup>†</sup>

|                  |                               |           |           |               | SERIES '16XXB/-15 |

|------------------|-------------------------------|-----------|-----------|---------------|-------------------|

| SYMBOL           | PARAMETER                     | EP330-12C | EP330-15C | 'PAL16L8B/-15 | 'PAL16R8B/-15     |

| loc              | Supply current active         | 75 mA     | 75 mA     | 180 mA        | 180 mA            |

| t <sub>pd</sub>  | Input to nonregistered output | 12 ns     | 15 ns     | 15 ns         | N/A               |

| <sup>t</sup> CO1 | Clock to output delay         | 8 ns      | 10 ns     | N/A           | 12 ns             |

| t <sub>eu</sub>  | Input setup time              | 6 ns      | 8 ns      | N/A           | 15 ns             |

| fmax             | Max frequency                 | 125 MHz   | 100 MHz   | N/A           | 37 MHz            |

Over commercial temperature range

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub> (see Note 1)              | 0.3 V to 7 V      |

|-----------------------------------------------------------------|-------------------|

| Instantaneous supply voltage range, V <sub>CC</sub> (t ≤ 20 ns) | –2 V to 7 V       |

| Programming supply voltage range, Vpp                           |                   |

| Instantaneous programming supply voltage range, Vpp (t ≤ 20 ns) | –2 V to 14 V      |

| Input voltage range, V <sub>1</sub>                             |                   |

| Instantaneous input voltage range, V <sub>I</sub> (t ≤ 20 ns)   | –2 V to 7 V       |

| V <sub>CC</sub> or GND current range                            | –160 mA to 160 mA |

| Operating free-air temperature range, T <sub>A</sub>            |                   |

| Storage temperature range                                       |                   |

NOTE 1: All voltage values are with respect to GND terminal.

# EP330-12C, EP330-15C HIGH-PERFORMANCE 8-MACROCELL ONE-TIME PROGRAMMABLE LOGIC DEVICES SRES002A - D3374, OCTOBER 1989 - REVISED SEPTEMBER 1992

# recommended operating conditions

|                 |                                      | EP3  | P330-12C EP3         |            | 30-15C               | LINE |

|-----------------|--------------------------------------|------|----------------------|------------|----------------------|------|

|                 |                                      | MIN  | MAX                  | MIN        | MAX                  | UNIT |

| V <sub>CC</sub> | Supply voltage                       | 4.75 | 5.25                 | 4.75       | 5.25                 | ٧    |

| VI              | Input voltage                        | 0    | Vcc                  | 0          | Vcc                  | V    |

| VIH             | High-level input voltage             | 2    | V <sub>CC</sub> +0.3 | 2          | V <sub>CC</sub> +0.3 | V    |

| VIL             | Low-level input voltage (see Note 2) | -0.3 | 0.8                  | -0.3       | 0,8                  | v    |

| Vo              | Output voltage                       | 0    | Vcc                  | 0          | Vcc                  | ·    |

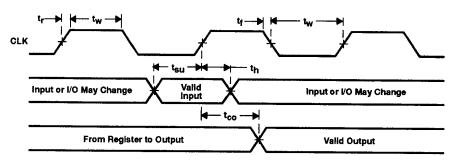

| t <sub>w</sub>  | Pulse duration, CLK high or low      | 4    |                      | 5          |                      | ns   |

| t <sub>su</sub> | Setup time, input                    | 6    |                      | 8          |                      | ns   |

| th              | Hold time, input                     | 0    |                      | 0          |                      | ns   |

| tr              | Rise time, input                     |      | 20                   | <u>-</u> _ | 20                   | ns   |

| tf              | Fall time, input                     |      | 20                   |            | 20                   | ns   |

| TA              | Operating free-air temperature       |      | 70                   | 0          | 70                   | °C   |

NOTE 2: The algebraic convention, in which the more negative value is designated minimum, is used in this data sheet for logic voltage levels

# electrical characteristics over recommended ranges of supply voltage and free-air temperature (unless otherwise noted)

| PARAMETER        |                           | TEST CONDITIONS              |                       | EP330-12C<br>EP330-15C         |              |     | UNIT |     |

|------------------|---------------------------|------------------------------|-----------------------|--------------------------------|--------------|-----|------|-----|

|                  |                           |                              |                       |                                | MIN          | TYP | MAX  |     |

| Vон              | High-level output voltage | V <sub>CC</sub> = 4.75 V,    | IOH = -12             | 2 mA                           | 2.4          |     |      | V   |

| VOL              | Low-level output voltage  | $V_{CC} = 4.75 \text{ V},$   | loL = 24 r            | nA                             | <b>†</b>     |     | 0.5  | l v |

| lį               | Input current             | V <sub>I</sub> = 5.25 V or 0 | GND                   |                                |              |     | ±10  | μА  |

| loz              | Off-state output current  | V <sub>CC</sub> = 5.25 V,    | Vo = Vcc              | or GND                         | <del></del>  |     | ±10  | μА  |

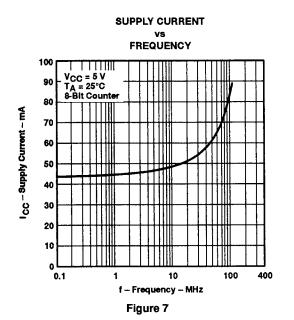

| <u>0</u>         | Supply current            | f = 1 MHz,                   | No load,              | Programmed as an 8-bit counter |              | 45  | 75   | mA  |

| c <sub>i</sub> ‡ | Input capacitance         | V <sub>CC</sub> = 5 V,       | V <sub>I</sub> = 0,   | f = 1 MHz                      | <del> </del> |     | 10   | pF  |

| Co               | Output capacitance        | V <sub>CC</sub> = 5 V,       | V <sub>O</sub> = 0.   | f = 1 MHz                      | +            |     | 15   | ρF  |

| C <sub>clk</sub> | Clock capacitance         | V <sub>CC</sub> = 5 V,       | V <sub>CLK</sub> = 0, |                                | +            |     | 10   | ρF  |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C. ‡ The input capacitance at pin 11 is 20 pF maximum when used as a programming pin and with Vpp = 14 V.

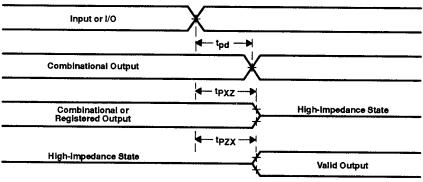

# switching characteristics over recommended ranges of supply voltage and operating free-air temperature (see Figure 5)

|                   |                                                |                             | EP330 | EP330-12C |      | )-15C | UNIT |

|-------------------|------------------------------------------------|-----------------------------|-------|-----------|------|-------|------|

|                   | PARAMETER <sup>†</sup> With no feedback        |                             | MIN   | MAX       | MIN  | MAX   | ONLI |

| •                 |                                                | With no feedback            | 125   |           | 100  |       |      |

| fmax <sup>‡</sup> | Maximum frequency                              | With internal feedback      | 100   |           | 100  |       | MHz  |

| ,,,,,,,,          |                                                | With external feedback      | 71.4  |           | 55.6 | 0     |      |

| <sup>t</sup> pd1  | input to nonregistered of                      | output delay (see Note 3)   |       | 12        |      | 15    | ns   |

| tpd2              | I/O to nonregistered output delay (see Note 3) |                             |       | 13        |      | 16    | ns   |

| tio               | I/O input and buffer del                       | ay (see Note 3)             |       | 1         |      | 1     | กร   |

| t <sub>co</sub>   | Clock input to registere                       | d output delay (see Note 3) |       | 8         |      | 10    | ns   |

| tPZX              | Output enable time (se                         | ee Note 4)                  |       | 12        |      | 15    | ns   |

| tPXZ              | Output disable time (se                        | ee Note 4)                  |       | 12        |      | 15    | ns   |

| tont              | Minimum clock period (                         | (internal)                  |       | 10        |      | 12    | ns   |

<sup>†</sup> Letter symbols for switching characteristics and timing requirements in this data sheet have been chosen for compatibility with those used in other documentation previously prepared by another supplier for similar products. Any similarity to symbols used on other Ti data sheets or to those shown in glossaries in Ti data books is coincidental. The meanings may not be the same.

$$\ddagger$$

f<sub>max</sub> with no feedback =  $\frac{1}{t_W \text{ high } + t_W \text{ low}}$ , f<sub>max</sub> with internal feedback =  $\frac{1}{t_{cnt}}$ ,

$$f_{max}$$

with external feedback =  $\frac{1}{t_{su} + t_{co}}$ .

fmax with internal feedback is programmed as an 8-bit counter.

NOTES: 3. This parameter is measured with only one output switching.

4. This is for an output voltage change of 500 mV.

# EP330-251 HIGH-PERFORMANCE 8-MACROCELL ONE-TIME PROGRAMMABLE LOGIC DEVICES

SRES002A - D3374, OCTOBER 1989 - REVISED SEPTEMBER 1992

# recommended operating conditions

|                 |                                      | MIN  | MAX                  | UNIT |

|-----------------|--------------------------------------|------|----------------------|------|

| Vcc             | Supply voltage                       | 4.5  | 5.5                  | V    |

| VĮ              | Input voltage                        | 0    | Vcc                  | V    |

| VIH             | High-level input voltage             | 2    | V <sub>CC</sub> +0.3 | V    |

| ٧ <sub>IL</sub> | Low-level input voltage (see Note 2) | -0.3 | 0.8                  | V    |

| Vo              | Output voltage                       | 0    | Vcc                  | V    |

| tw              | Pulse duration, CLK high or low      | 12   |                      | ns   |

| tsu             | Setup time, input                    | 15   | ~                    | ns   |

| th              | Hold time, input                     | 0    |                      | ns   |

| tr              | Rise time, input                     |      | 20                   | กร   |

| tf              | Fall time, input                     |      | 20                   | ns   |

| TA              | Operating free-air temperature       | -40  | 85                   | °C   |

NOTE 2: The algebraic convention, in which the more negative value is designated minimum, is used in this data sheet for logic voltage levels only.

# electrical characteristics over recommended ranges of supply voltage and free-air temperature (unless otherwise noted)

|                  | PARAMETER                 | TEST CONDITIONS                                                  |                  | MIN | TYP | MAX | UNIT |

|------------------|---------------------------|------------------------------------------------------------------|------------------|-----|-----|-----|------|

| Vон              | High-level output voltage | V <sub>CC</sub> = 4.5 V, I <sub>OH</sub> = -12 mA                |                  | 2.4 |     |     | V    |

| VoL              | Low-level output voltage  | V <sub>CC</sub> = 4.5 V, I <sub>OL</sub> = 24 mA                 |                  |     |     | 0.5 | V    |

| lj .             | Input current             | V <sub>I</sub> = 5.5 V or GND                                    |                  |     |     | ±10 | μА   |

| loz              | Off-state output current  | V <sub>CC</sub> = 5.5 V, V <sub>O</sub> = V <sub>CC</sub> or GND |                  |     |     | ±10 | μА   |

| Icc              | Supply current            | f = 1 MHz, No load, Programmed as a                              | ın 8-bit counter |     | 45  | 75  | mA   |

| Ci               | Input capacitance         | V <sub>CC</sub> = 5 V, V <sub>I</sub> = 2 V, f = 1 MHz           |                  |     |     | 10  | pF   |

| Co               | Output capacitance        | V <sub>CC</sub> = 5 V, V <sub>O</sub> = 2 V, f = 1 MHz           |                  |     |     | 15  | ρF   |

| C <sub>clk</sub> | Clock capacitance         | V <sub>CC</sub> = 5 V, V <sub>CLK</sub> = 2 V, f = 1 MHz         |                  |     |     | 10  | pF   |

# switching characteristics over recommended ranges of supply voltage and operating free-air temperature (see Figure 5)

|                                                | PARAMETER <sup>‡</sup>                                                                                                                                | MIN                                                                                                                                                                                                                                                                                                               | MAX                                                                                                                                                                                                                                                                                                                                                                  | UNIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                | With no feedback                                                                                                                                      | 41.6                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Maximum frequency With internal feedback       | 41.6                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                   | MHz                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                | With external feedback                                                                                                                                | 28.5                                                                                                                                                                                                                                                                                                              | 25<br>26<br>1<br>15<br>25<br>25                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| input to nonregistered of                      | output delay (see Note 3)                                                                                                                             |                                                                                                                                                                                                                                                                                                                   | 25                                                                                                                                                                                                                                                                                                                                                                   | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| I/O to nonregistered output delay (see Note 3) |                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                   | 26                                                                                                                                                                                                                                                                                                                                                                   | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| I/O input and buffer delay (see Note 3)        |                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Clock input to registere                       | d output delay (see Note 3)                                                                                                                           |                                                                                                                                                                                                                                                                                                                   | 15                                                                                                                                                                                                                                                                                                                                                                   | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Output enable time (se                         | e Note 4)                                                                                                                                             |                                                                                                                                                                                                                                                                                                                   | 25                                                                                                                                                                                                                                                                                                                                                                   | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CZ Output disable time (see Note 4)            |                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                   | 25                                                                                                                                                                                                                                                                                                                                                                   | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Minimum clock period (                         | internal)                                                                                                                                             |                                                                                                                                                                                                                                                                                                                   | 24                                                                                                                                                                                                                                                                                                                                                                   | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                | input to nonregistered of I/O to nonregistered of I/O input and buffer dell Clock input to registere Output enable time (see Output disable time (see | Maximum frequency  With no feedback With internal feedback With external feedback Input to nonregistered output delay (see Note 3)  I/O to nonregistered output delay (see Note 3)  I/O input and buffer delay (see Note 3)  Clock input to registered output delay (see Note 3)  Output enable time (see Note 4) | With no feedback 41.6  Maximum frequency With internal feedback 41.6  With external feedback 28.5  Input to nonregistered output delay (see Note 3)  I/O to nonregistered output delay (see Note 3)  I/O input and buffer delay (see Note 3)  Clock input to registered output delay (see Note 3)  Output enable time (see Note 4)  Output disable time (see Note 4) | With no feedback   41.6   With internal feedback   With internal feedback   With external feedback   28.5   With external feedback   With external feedback   28.5   With external feedback |

TAll typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

Letter symbols for switching characteristics and timing requirements in this data sheet have been chosen for compatibility with those used in other documentation previously prepared by another supplier for similar products. Any similarity to symbols used on other TI data sheets or to those shown in glossaries in TI data books is coincidental. The meanings may not be the same.

fmax with no feedback =

$$\frac{1}{\text{tw high + tw low}}$$

, fmax with internal feedback =  $\frac{1}{\text{tent}}$

$$f_{max}$$

with external feedback =  $\frac{1}{t_{su} + t_{co}}$ .

fmax with internal feedback is programmed as an 8-bit counter.

NOTES: 3. This parameter is measured with only one output switching.

4. This is for an output voltage change of 500 mV.

PRODUCT PREVIEW Information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas instruments reserves the right to change or discontinue these products without notice.

# PARAMETER MEASUREMENT INFORMATION

# functional testing

The EP330 is functionally tested through complete testing of each programmable EPROM bit and all internal logic elements, thus ensuring 100% programming yield.

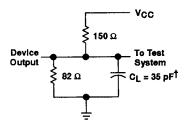

<sup>†</sup> Includes probe and circuit capacitance. Equivalent loads may be used for testing.

Figure 5. Dynamic Test Circuit

# design security

The EP330 contains a programmable design-security feature that controls the access to the data programmed into the device. If this programmable feature is used, a proprietary design implemented in the device cannot be copied or retrieved. Therefore, a very high level of design control is achieved since programmed data within EPROM cells is invisible. The bit that controls this function, along with all other program data, may be reset by erasing the cells in the device.

#### latch-up

The EP330 input, I/O, and clock pins have been carefully designed to resist the latch-up that is inherent in CMOS structures. The EP330 pins will not latch up for input voltages between -1 V and  $V_{CC}$  + 1 V with currents up to 250 mA. During transitions, the inputs may undershoot to -2 V for periods of less than 20 ns.

Although the programming pin (pin 11) is designed to resist latch-up to the 13.5-V limit, during positive-current latch-up testing, the verify mode (pin 1) and program mode (pin 11) can be inadvertently entered into, causing current flow in the pins. This should not be construed as latch-up.

# PARAMETER MEASUREMENT INFORMATION

# (a) COMBINATIONAL MODE

(b) SYNCHRONOUS CLOCK MODE

NOTES: A. Rise time  $(t_f)$  and fail time  $(t_f) < 3$  ns

- B. twis measured at 0.3 V and 2.7 V. All other timing is measured at 1.5 V, except tpzx and tpxz which are measured for an output voltage change of 500 mV.

- C. Input voltage levels at 0 V and 3 V

Figure 6. Voltage Waveforms

### TYPICAL CHARACTERISTICS

**CHANGE IN PROPAGATION DELAY TIME** VS LOAD CAPACITANCE 13 VCC = 5 V 12 T<sub>A</sub> = 25°C R1 = 150 Ω 11  $R2 = 82 \Omega$ 10 Change in Propagation Delay Time t<sub>PHI</sub> 9 8 7 6 5 <sup>t</sup>PLH 3 2 0 100 300 400 500 600 700 CL - Load Capacitance - pF

Figure 8

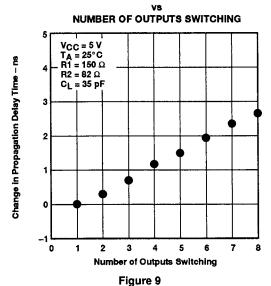

## **CHANGE IN PROPAGATION DELAY TIME**