# **Section 1. Device Core**

This section provides a complete overview of all features relating to the Cyclone<sup>®</sup> IV device family, which is the most architecturally advanced, high-performance, low-power FPGA in the market place. This section includes the following chapters:

- Chapter 1, Cyclone IV FPGA Device Family Overview

- Chapter 2, Logic Elements and Logic Array Blocks in Cyclone IV Devices

- Chapter 3, Memory Blocks in Cyclone IV Devices

- Chapter 4, Embedded Multipliers in Cyclone IV Devices

- Chapter 5, Clock Networks and PLLs in Cyclone IV Devices

## **Revision History**

Refer to each chapter for its own specific revision history. For information about when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

# 1. Cyclone IV FPGA Device Family Overview

Altera's new Cyclone<sup>®</sup> IV FPGA device family extends the Cyclone FPGA series leadership in providing the market's lowest-cost, lowest-power FPGAs, now with a transceiver variant. Cyclone IV devices are targeted to high-volume, cost-sensitive applications, enabling system designers to meet increasing bandwidth requirements while lowering costs.

Built on an optimized low-power process, the Cyclone IV device family offers the following two variants:

- Cyclone IV E—lowest power, high functionality with the lowest cost

- Cyclone IV GX—lowest power and lowest cost FPGAs with 3.125 Gbps transceivers

Providing power and cost savings without sacrificing performance, along with a low-cost integrated transceiver option, Cyclone IV devices are ideal for low-cost, small-form-factor applications in the wireless, wireline, broadcast, industrial, consumer, and communications industries.

# **Cyclone IV Device Family Features**

The Cyclone IV device family offers the following features:

- Low cost, low power FPGA fabric:

- 6K to 155K logic elements

- Up to 6 Mb of embedded memory

- Up to 360 18 × 18 multipliers for DSP processing intensive applications

- Protocol bridging applications for under 1.5 W total power

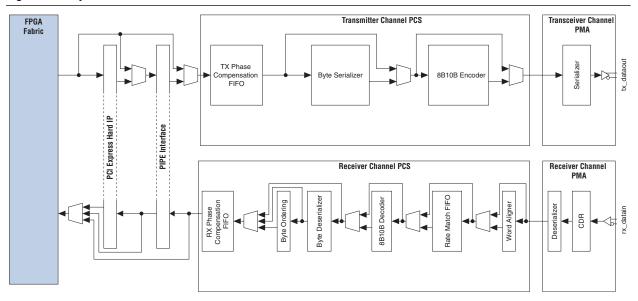

- Cyclone IV GX devices offer up to eight high-speed transceivers that provide:

- Data rates up to 3.125 Gbps

- 8B10B encoder/decoder

- 8-bit or 10-bit PMA to PCS interface

- Byte serializer/deserializer

- Word aligner

- Rate matching FIFO

- TX bit slipper for CPRI

- Electrical idle

- Dynamic channel reconfiguration allowing you to change data rates and protocols on-the-fly

- Static equalization and pre-emphasis for superior signal integrity

- 150 mW per channel power consumption

- Flexible clocking structure to support multiple protocols in a single transceiver block

- Cyclone IV GX devices offer dedicated Hard IP for PCI Express Gen 1:

- ×1, ×2, and ×4 lane configurations

- End point and root port configurations

- Up to 256-byte payload

- One virtual channel

- 2 KB retry buffer

- 4 KB RX buffer

- Cyclone IV GX devices offer a wide range of protocol support:

- PCI Express Gen 1 ×1, ×2, and ×4 (2.5 Gbps)

- Gigabit Ethernet (1.25 Gbps)

- Common Public Radio Interface (CPRI) (up to 3.072 Gbps)

- XAUI (3.125 Gbps)

- Triple rate Serial Digital Interface (SDI) (up to 2.97 Gbps)

- Serial RapidIO (3.125 Gbps)

- Basic mode (up to 3.125 Gbps)

- V-by-One (up to 3.0 Gbps)

- DisplayPort (2.7 Gbps)

- SATA (up to 3.0 Gbps)

- Up to 535 user I/Os

- LVDS interfaces up to 840 Mbps TX, 875 Mbps RX

- Support for DDR2 SDRAM interfaces up to 200 MHz

- Support for QDRII SRAM and DDR SDRAM up to 167 MHz

- Up to eight PLLs per device

- Offered in commercial and industrial temperature grades

# **Device Resources**

Table 1–1 shows Cyclone IV E device resources.

Table 1–1. Cyclone IV E Device Resources

| Resources                    | EP4CE6 | EP4CE10 | EP4CE15 | EP4CE30 | EP4CE40 | EP4CE55 | EP4CE75 | EP4CE115 |

|------------------------------|--------|---------|---------|---------|---------|---------|---------|----------|

| Logic elements (LEs)         | 6,272  | 10,320  | 15,408  | 28,848  | 39,600  | 55,856  | 75,408  | 114,480  |

| Embedded memory (Kbits)      | 270    | 414     | 504     | 594     | 1,134   | 2,340   | 2,745   | 3,888    |

| Embedded 18 × 18 multipliers | 15     | 23      | 56      | 66      | 116     | 154     | 200     | 266      |

| General-purpose PLLs         | 2      | 2       | 4       | 4       | 4       | 4       | 4       | 4        |

| Maximum user I/O             | 182    | 182     | 346     | 535     | 535     | 377     | 429     | 531      |

Table 1–2 shows Cyclone IV GX device resources.

| Table 1-2. | Cyclone | IV GX | Device | Resources |

|------------|---------|-------|--------|-----------|

|------------|---------|-------|--------|-----------|

| Resources                               | EP4CGX15     | EP4CGX22     | EP4CGX30     | EP4CGX50      | EP4CGX75      | EP4CGX110     | EP4CGX150 |

|-----------------------------------------|--------------|--------------|--------------|---------------|---------------|---------------|-----------|

| Logic elements (LEs)                    | 14,400       | 21,280       | 29,440       | 49,888        | 73,920        | 109,424       | 149,760   |

| Embedded memory (Kbits)                 | 540          | 756          | 1,080        | 2,502         | 4,158         | 5,490         | 6,480     |

| Embedded 18 × 18 multipliers            | 0            | 40           | 80           | 140           | 198           | 280           | 360       |

| General-purpose PLLs (GPLLs)            | 1            | 2            | 2            | 4 (2)         | 4 (2)         | 4 (2)         | 4 (2)     |

| Multi-purpose PLLs (MPLLs)              | 2 (1)        | 2 (1)        | 2 (1)        | 4 (1)         | 4 (1)         | 4 (1)         | 4 (1)     |

| Global clock networks                   | 20           | 20           | 20           | 30            | 30            | 30            | 30        |

| High-speed transceivers (5)             | 2            | 4            | 4            | 8             | 8             | 8             | 8         |

| Transceiver maximum data rate<br>(Gbps) | 2.5          | 2.5          | 2.5          | 3.125         | 3.125         | 3.125         | 3.125     |

| PCI Express Hard IP blocks              | 1            | 1            | 1            | 1             | 1             | 1             | 1         |

| User I/O banks                          | 9 <i>(3)</i> | 9 <i>(3)</i> | 9 <i>(3)</i> | 11 <i>(4)</i> | 11 <i>(4)</i> | 11 <i>(4)</i> | 11 (4)    |

| Maximum user I/O                        | 72           | 150          | 150          | 310           | 310           | 475           | 475       |

Notes to Table 1-2:

(1) The MPLLs can be used for general purpose clocking when not used to clock the transceivers. For more information, refer to the *Clock Networks* and *PLLs in Cyclone IV Devices* chapter.

(2) Two of the GPLLs are able to support the transceiver clocking. For more information, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

(3) Including one Configuration I/O bank and two dedicated Clock input I/O banks for HSSI reference Clock input.

(4) Including one Configuration I/O bank and four dedicated Clock input I/O banks for HSSI reference Clock input.

(5) If PCIe X1 is implemented, the remaining transceivers in a quad can be used for other protocols at the same or different data rates.

# Package Matrix

Table 1–3 shows Cyclone IV E device package offerings.

| <b>Idule 1-3.</b> Cyclulle IV E Device Fackage Unerlings | 3. Cyclone IV E Device Package Offerings | Table 1–3. |

|----------------------------------------------------------|------------------------------------------|------------|

|----------------------------------------------------------|------------------------------------------|------------|

| Package    | E144     |      | F2           | 56   | F4          | 84   | F780     |         |  |  |  |

|------------|----------|------|--------------|------|-------------|------|----------|---------|--|--|--|

| Size (mm)  | 22 :     | × 22 | 17 >         | « 17 | 23 :        | × 23 | 29 :     | 29 × 29 |  |  |  |

| Pitch (mm) | 0        | .5   | 1.           | .0   | 1.          | .0   | 1.0      |         |  |  |  |

| Device     | User I/O | LVDS | User I/O     | LVDS | User I/O    | LVDS | User I/O | LVDS    |  |  |  |

| EP4CE6     | 94       | 22   | <b>♦</b> 182 | 68   | —           | —    | —        | —       |  |  |  |

| EP4CE10    | 94       | 22   | 182          | 68   | —           | _    | —        |         |  |  |  |

| EP4CE15    | ·        | _    | 168          | 55   | ▲ 346       | 140  | —        |         |  |  |  |

| EP4CE30    |          | _    | _            | _    | 331         | 127  | ◆ 535    | 227     |  |  |  |

| EP4CE40    |          | —    | —            | —    | 331         | 127  | 535      | 227     |  |  |  |

| EP4CE55    | —        | —    | -            | —    | <b>3</b> 27 | 135  | 377      | 163     |  |  |  |

| EP4CE75    | _        | —    | _            | —    | 295         | 113  | 429      | 181     |  |  |  |

| EP4CE115   | _        | _    | _            | _    | 283         | 106  | 531      | 233     |  |  |  |

Table 1–4.

Cyclone IV GX Device Package Offerings

| Package    |          | N148   |       |          | F169    |           |          | F324 |                 |          | F484 |       |          | F672 |       |          | F896 |       |

|------------|----------|--------|-------|----------|---------|-----------|----------|------|-----------------|----------|------|-------|----------|------|-------|----------|------|-------|

| Size (mm)  | 1        | 1 × 11 |       | •        | 14 × 14 | 4 19 × 19 |          |      | 23 × 23 27 × 27 |          |      |       | 31 × 31  |      |       |          |      |       |

| Pitch (mm) |          | 0.5    |       |          | 1.0     |           |          | 1.0  |                 |          | 1.0  |       |          | 1.0  |       |          | 1.0  |       |

| Device     | User I/O | LVDS   | XCVRs | User I/O | LVDS    | XCVRs     | User I/O | LVDS | XCVRs           | User I/O | LVDS | XCVRs | User I/O | LVDS | XCVRs | User I/O | LVDS | XCVRs |

| EP4CGX15   | 72       | 25     | 2     | 72       | 25      | 2         | _        | —    | _               | —        | —    | —     | —        | —    | _     | —        | —    | —     |

| EP4CGX22   | _        | _      | —     | 72       | 25      | 2         | 150      | 64   | 4               | _        | —    | —     | _        | —    | _     | _        | —    | —     |

| EP4CGX30   | _        | _      | —     | 72       | 25      | 2         | 150      | 64   | 4               | _        | —    | —     | _        | _    | _     | _        | —    | _     |

| EP4CGX50   | _        | _      | —     | _        | —       | —         | _        | —    | _               | 290      | 109  | 4     | 310      | 140  | 8     | _        | —    | _     |

| EP4CGX75   |          | _      |       | _        | —       | —         | _        | —    | —               | 290      | 109  | 4     | 310      | 140  | 8     | _        | —    | _     |

| EP4CGX110  |          |        | _     | _        | —       | _         |          | —    | _               | 270      | 93   | 4     | 393      | 152  | 8     | 475      | 216  | 8     |

| EP4CGX150  |          | _      | —     | _        | —       | —         |          | -    | _               | 270      | 93   | 4     | 393      | 152  | 8     | 475      | 216  | 8     |

Chapter 1: Cyclone IV FPGA Device Family Overview Package Matrix

# **Cyclone IV Device Family Architecture**

This section discusses Cyclone IV device architecture and contains the following topics:

- "FPGA Core Fabric"

- "I/O Features"

- "Clock Management"

- "External Memory Interfaces"

- "Configuration"

- "High-Speed Transceivers (Cyclone IV GX Devices Only)"

- "Hard IP for PCI Express (Cyclone IV GX Devices Only)"

#### **FPGA Core Fabric**

Cyclone IV devices leverage the same core fabric as the very successful Cyclone series devices. The fabric consists of LEs, made of 4-input look up tables (LUTs), memory blocks, and multipliers.

Each Cyclone IV device M9K memory block provides 9 Kbits of embedded SRAM memory. The M9K blocks can be configured as single port, simple dual port, or true dual port RAM, as well as FIFO buffers or ROM. They can also be configured to implement any of the data widths in Table 1–5.

Table 1–5. Cyclone IV Device M9K Block Data Widths

| Mode                            | Data Width Configurations            |

|---------------------------------|--------------------------------------|

| Single port or simple dual port | ×1, ×2, ×4, ×8/9, ×16/18, and ×32/36 |

| True dual port                  | ×1, ×2, ×4, ×8/9, and ×16/18         |

The multiplier architecture in Cyclone IV devices is the same as in existing Cyclone series devices. The embedded multiplier blocks can implement an 18 × 18 or two 9 × 9 multipliers in a single block. Altera offers a complete suite of DSP IP including FIR, FFT, and NCO functions for use with the multiplier blocks. The Quartus® II design software's DSP Builder tool integrates MathWorks Simulink and MATLAB design environments for a streamlined DSP design flow.

### I/O Features

Cyclone IV device I/O supports programmable bus hold, programmable pull-up resistors, programmable delay, programmable drive strength, programmable slew-rate control to optimize signal integrity, and hot socketing. Cyclone IV devices support calibrated on-chip series termination (RS OCT) or driver impedance matching (Rs) for single-ended I/O standards. In Cyclone IV GX devices, the high-speed transceiver I/Os are located on the left side of the device. The top, bottom, and right sides can implement general-purpose user I/Os.

Table 1–6 lists the I/O standards that Cyclone IV devices support.

| ,                | · · · · · · · · · · · · · · · · · · ·                      |

|------------------|------------------------------------------------------------|

| Туре             | I/O Standard                                               |

| Single-Ended I/O | LVTTL, LVCMOS, SSTL, HSTL, PCI, and PCI-X                  |

| Differential I/O | SSTL, HSTL, LVPECL, BLVDS, LVDS, mini-LVDS, RSDS, and PPDS |

Table 1–6. Cyclone IV Device I/O Standards Support

The LVDS SERDES is implemented in the core of the device using logic elements.

#### **Clock Management**

Cyclone IV devices include up to 30 global clock networks and up to eight PLLs with five outputs per PLL to provide robust clock management and synthesis. Cyclone IV device PLLs can be dynamically reconfigured in user mode to change the clock frequency or phase.

Cyclone IV GX devices support two types of PLLs: Multi-purpose PLLs (MPLLs) and General-purpose PLLs (GPLLs):

- MPLLs are used for clocking the transceiver blocks. They can also be used for general-purpose clocking when not used for transceiver clocking.

- GPLLs can be used for general-purpose applications in the fabric and periphery, such as external memory interfaces. Some of the GPLLs can support the transceiver clocking. For more information, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

#### **External Memory Interfaces**

Cyclone IV devices support SDR, DDR, DDR2 SDRAM, and QDRII SRAM interfaces on the top, bottom, and right sides of the device. Cyclone IV E devices also support these interfaces on the left side of the device. Interfaces may span two or more sides of the device to allow more flexible board design. The Altera® DDR SDRAM memory interface solution consists of a PHY interface and a memory controller. The PHY IP is provided by Altera and can be used in conjunction with your own custom memory controller or an Altera-provided memory controller. Cyclone IV devices support use of ECC bits on DDR and DDR2 SDRAM interfaces.

#### Configuration

Cyclone IV devices use SRAM cells to store configuration data. Configuration data is downloaded to the Cyclone IV device each time the device powers up. Low-cost configuration options include the Altera EPCS family serial flash devices and commodity parallel flash configuration options. These options provide the flexibility for general-purpose applications and the ability to meet specific configuration and wake-up time requirements of the applications. Table 1–7 shows which configuration schemes are supported by Cyclone IV devices.

| Devices       | Supported Configuration Scheme |

|---------------|--------------------------------|

| Cyclone IV GX | AS, PS, JTAG, PP (1)           |

| Cyclone IV E  | AS, AP, PS, FPP, JTAG          |

Table 1–7. Cyclone IV Device Configuration Schemes

Note to Table 1–7:

(1) The PP configuration scheme is only supported by EP4CGX50/75/110/150 devices

IEEE 1149.6 (AC JTAG) is supported on all transceiver I/O pins. All other pins support IEEE 1149.1 (JTAG) for boundary scan testing.

For Cyclone IV GX devices to meet the PCIe 100 ms wake-up time requirement, you must use the PS configuration mode for EP4CGX15/22/30 devices and the PP configuration mode for EP4CGX50/75/110/150 devices.

## High-Speed Transceivers (Cyclone IV GX Devices Only)

Cyclone IV GX devices contain up to eight full duplex high-speed transceivers that can operate independently. These blocks support multiple industry-standard communication protocols, as well as Basic mode, which can be used to implement your own proprietary protocols. Each transceiver channel has its own pre-emphasis and equalization circuitry, which can be set at compile time to optimize signal integrity and reduce bit error rates. Transceiver blocks also support dynamic reconfiguration, allowing you to change data rates and protocols on-the-fly.

The block diagram in Figure 1–1 shows the structure of the Cyclone IV GX transceiver.

Figure 1–1. Cyclone IV GX Transceiver Channel

## Hard IP for PCI Express (Cyclone IV GX Devices Only)

Cyclone IV GX devices incorporate a single hard IP block for ×1, ×2, or ×4 PCI Express (PIPE) in each device. This hard IP block is a complete PCI Express (PIPE) protocol solution that implements PHY-MAC layer, Data Link Layer, and Transaction Layer functionality. The hard IP for the PCI Express block supports root port and end point configurations. This pre-verified hard IP block reduces risk, design time, timing closure, and verification. You can configure the block with the Quartus II software's PCI Express Compiler, which guides you through the process step by step.

# **Reference and Ordering Information**

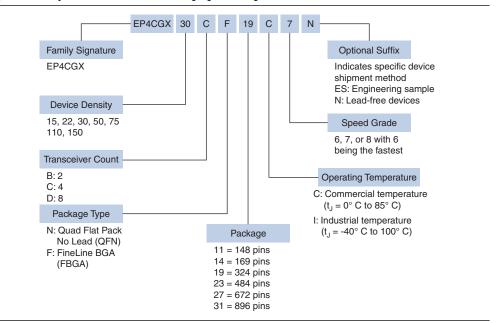

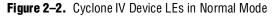

Figure 1–2 describes the ordering codes for Cyclone IV GX devices.

Figure 1–2. Cyclone IV GX Device Packaging Ordering Information

# **Chapter Revision History**

Table 1–8 shows the revision history for this chapter.

| Table 1-8. | Chapter Revision History |

|------------|--------------------------|

|------------|--------------------------|

| Date          | Version | Changes Made     |

|---------------|---------|------------------|

| November 2009 | 1.0     | Initial release. |

# 2. Logic Elements and Logic Array Blocks in Cyclone IV Devices

CYIV-51002-1.0

This chapter contains feature definitions for logic elements (LEs) and logic array blocks (LABs). Details are provided on how LEs work, how LABs contain groups of LEs, and how LABs interface with the other blocks in Cyclone® IV devices.

# **Logic Elements**

Logic elements (LEs) are the smallest units of logic in the Cyclone IV device architecture. LEs are compact and provide advanced features with efficient logic usage. Each LE has the following features:

- A four-input look-up table (LUT), which can implement any function of four variables

- A programmable register

- A carry chain connection

- A register chain connection

- The ability to drive the following interconnects:

- Local

- Row

- Column

- Register chain

- Direct link

- Register packing support

- Register feedback support

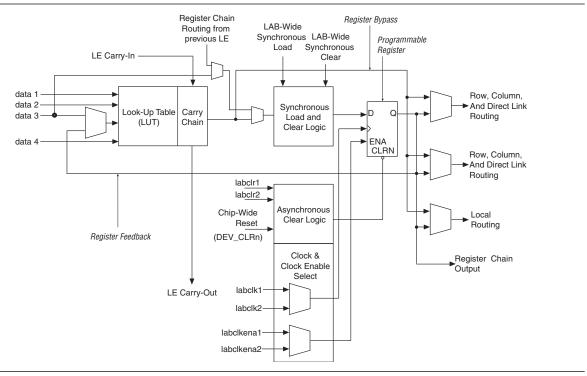

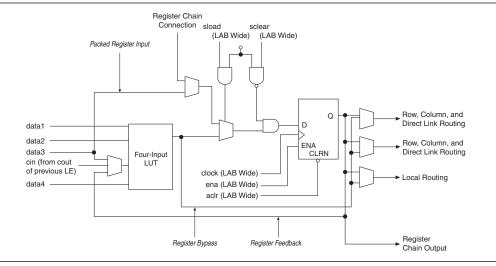

Figure 2-1 shows the LEs for Cyclone IV devices.

## **LE Features**

You can configure the programmable register of each LE for D, T, JK, or SR flipflop operation. Each register has data, clock, clock enable, and clear inputs. Signals that use the global clock network, general-purpose I/O pins, or any internal logic can drive the clock and clear control signals of the register. Either general-purpose I/O pins or the internal logic can drive the clock enable. For combinational functions, the LUT output bypasses the register and drives directly to the LE outputs.

Each LE has three outputs that drive the local, row, and column routing resources. The LUT or register output independently drives these three outputs. Two LE outputs drive the column or row and direct link routing connections, while one LE drives the local interconnect resources. This allows the LUT to drive one output while the register drives another output. This feature, called register packing, improves device utilization because the device can use the register and the LUT for unrelated functions. The LAB-wide synchronous load control signal is not available when using register packing. For more information about the synchronous load control signal, refer to "LAB Control Signals" on page 2–6.

The register feedback mode allows the register output to feed back into the LUT of the same LE to ensure that the register is packed with its own fan-out LUT, providing another mechanism for improved fitting. The LE can also drive out registered and unregistered versions of the LUT output.

In addition to the three general routing outputs, LEs in an LAB have register chain outputs, which allows registers in the same LAB to cascade together. The register chain output allows the LUTs to be used for combinational functions and the registers to be used for an unrelated shift register implementation. These resources speed up connections between LABs while saving local interconnect resources.

# **LE Operating Modes**

Cyclone IV LEs operate in the following modes:

- Normal mode

- Arithmetic mode

The Quartus® II software automatically chooses the appropriate mode for common functions, such as counters, adders, subtractors, and arithmetic functions, in conjunction with parameterized functions such as the library of parameterized modules (LPM) functions. You can also create special-purpose functions that specify which LE operating mode to use for optimal performance, if required.

### **Normal Mode**

Normal mode is suitable for general logic applications and combinational functions. In normal mode, four data inputs from the LAB local interconnect are inputs to a four-input LUT (Figure 2–2). The Quartus II Compiler automatically selects the carry-in (cin) or the data3 signal as one of the inputs to the LUT. LEs in normal mode support packed registers and register feedback.

Figure 2–2 shows LEs in normal mode.

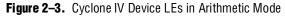

### **Arithmetic Mode**

Arithmetic mode is ideal for implementing adders, counters, accumulators, and comparators. An LE in arithmetic mode implements a 2-bit full adder and basic carry chain (Figure 2–3). LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output. Register feedback and register packing are supported when LEs are used in arithmetic mode.

Figure 2–3 shows LEs in arithmetic mode.

The Quartus II Compiler automatically creates carry chain logic during design processing. You can also manually create the carry chain logic during design entry. Parameterized functions, such as LPM functions, automatically take advantage of carry chains for the appropriate functions.

The Quartus II Compiler creates carry chains longer than 16 LEs by automatically linking LABs in the same column. For enhanced fitting, a long carry chain runs vertically, which allows fast horizontal connections to M9K memory blocks or embedded multipliers through direct link interconnects. For example, if a design has a long carry chain in an LAB column next to a column of M9K memory blocks, any LE output can feed an adjacent M9K memory block through the direct link interconnect. If the carry chains run horizontally, any LAB which is not next to the column of M9K memory blocks uses other row or column interconnects to drive a M9K memory block. A carry chain continues as far as a full column.

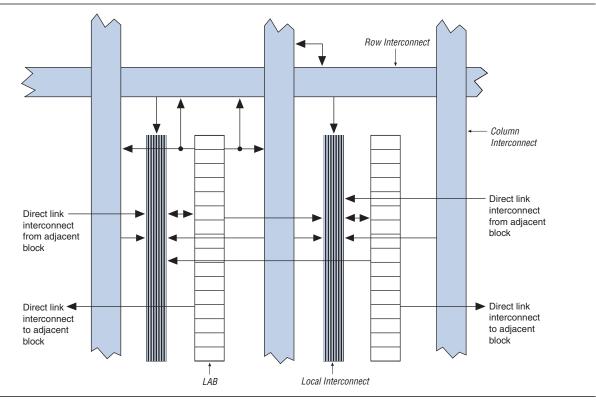

## **Logic Array Blocks**

Logic array blocks (LABs) contain groups of LEs.

### Topology

Each LAB consists of the following features:

16 LEs

- LAB control signals

- LE carry chains

- Register chains

- Local interconnect

The local interconnect transfers signals between LEs in the same LAB. Register chain connections transfer the output of one LE register to the adjacent LE register in an LAB. The Quartus II Compiler places associated logic in an LAB or adjacent LABs, allowing the use of local and register chain connections for performance and area efficiency.

Figure 2–4 shows the LAB structure for Cyclone IV devices.

Figure 2–4. Cyclone IV Device LAB Structure

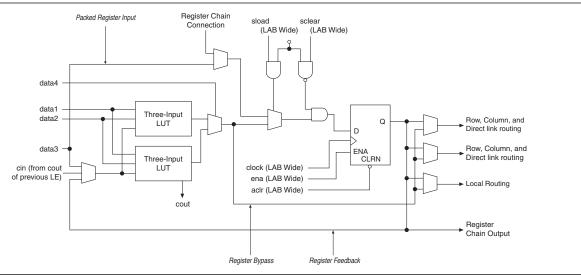

### **LAB Interconnects**

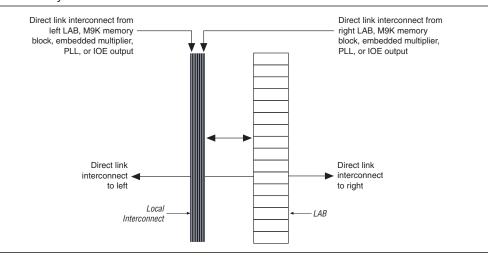

The LAB local interconnect is driven by column and row interconnects and LE outputs in the same LAB. Neighboring LABs, phase-locked loops (PLLs), M9K RAM blocks, and embedded multipliers from the left and right can also drive the local interconnect of a LAB through the direct link connection. The direct link connection feature minimizes the use of row and column interconnects, providing higher performance and flexibility. Each LE can drive up to 48 LEs through fast local and direct link interconnects.

Figure 2–5 shows the direct link connection.

Figure 2–5. Cyclone IV Device Direct Link Connection

## **LAB Control Signals**

Each LAB contains dedicated logic for driving control signals to its LEs. The control signals include:

- Two clocks

- Two clock enables

- Two asynchronous clears

- One synchronous clear

- One synchronous load

You can use up to eight control signals at a time. Register packing and synchronous load cannot be used simultaneously.

Each LAB can have up to four non-global control signals. You can use additional LAB control signals as long as they are global signals.

Synchronous clear and load signals are useful for implementing counters and other functions. The synchronous clear and synchronous load signals are LAB-wide signals that affect all registers in the LAB.

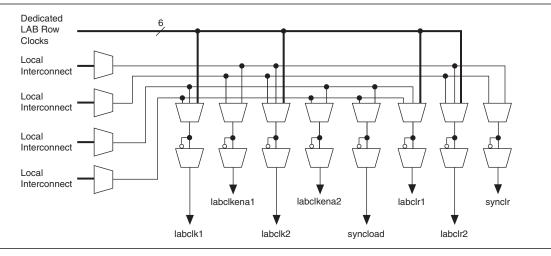

Each LAB can use two clocks and two clock enable signals. The clock and clock enable signals of each LAB are linked. For example, any LE in a particular LAB using the labclk1 signal also uses the labclkena1. If the LAB uses both the rising and falling edges of a clock, it also uses both LAB-wide clock signals. Deasserting the clock enable signal turns off the LAB-wide clock.

The LAB row clocks [5..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack interconnect inherent low skew allows clock and control signal distribution in addition to data distribution.

Figure 2–6 shows the LAB control signal generation circuit.

Figure 2–6. Cyclone IV Device LAB-Wide Control Signals

LAB-wide signals control the logic for the clear signal of the register. The LE directly supports an asynchronous clear function. Each LAB supports up to two asynchronous clear signals (labclr1 and labclr2).

A LAB-wide asynchronous load signal to control the logic for the preset signal of the register is not available. The register preset is achieved with a NOT gate push-back technique. Cyclone IV devices only support either a preset or asynchronous clear signal.

In addition to the clear port, Cyclone IV devices provide a chip-wide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This chip-wide reset overrides all other control signals.

# **Chapter Revision History**

Table 2–1 shows the revision history for this chapter.

| Table 2–1. | Chapter Revision History | 1 |

|------------|--------------------------|---|

|------------|--------------------------|---|

| Date          | Version | Changes Made     |  |  |  |

|---------------|---------|------------------|--|--|--|

| November 2009 | 1.0     | Initial release. |  |  |  |

# 3. Memory Blocks in Cyclone IV Devices

Cyclone<sup>®</sup> IV devices feature embedded memory structures to address the on-chip memory needs of Altera<sup>®</sup> Cyclone IV device designs. The embedded memory structure consists of columns of M9K memory blocks that you can configure to provide various memory functions, such as RAM, shift registers, ROM, and FIFO buffers.

This chapter contains the following sections:

- "Memory Modes" on page 3–7

- "Clocking Modes" on page 3–14

- "Design Considerations" on page 3–15

## **Overview**

M9K blocks support the following features:

- 8,192 memory bits per block (9,216 bits per block including parity)

- Independent read-enable (rden) and write-enable (wren) signals for each port

- Packed mode in which the M9K memory block is split into two 4.5 K single-port RAMs

- Variable port configurations

- Single-port and simple dual-port modes support for all port widths

- True dual-port (one read and one write, two reads, or two writes) operation

- Byte enables for data input masking during writes

- Two clock-enable control signals for each port (port A and port B)

- Initialization file to pre-load memory content in RAM and ROM modes

Table 3–1 lists the features supported by the M9K memory.

Table 3–1.

Summary of M9K Memory Features

| Feature                                | M9K Blocks                                       |  |  |  |  |

|----------------------------------------|--------------------------------------------------|--|--|--|--|

|                                        | 8192 × 1                                         |  |  |  |  |

|                                        | 4096 × 2                                         |  |  |  |  |

|                                        | 2048 × 4                                         |  |  |  |  |

|                                        | 1024 × 8                                         |  |  |  |  |

| Configurations (depth × width)         | 1024 × 9                                         |  |  |  |  |

|                                        | 512 × 16                                         |  |  |  |  |

|                                        | 512 × 18                                         |  |  |  |  |

|                                        | 256 × 32                                         |  |  |  |  |

|                                        | 256 × 36                                         |  |  |  |  |

| Parity bits                            | $\checkmark$                                     |  |  |  |  |

| Byte enable                            | $\checkmark$                                     |  |  |  |  |

| Packed mode                            | $\checkmark$                                     |  |  |  |  |

| Address clock enable                   | $\checkmark$                                     |  |  |  |  |

| Single-port mode                       | ✓                                                |  |  |  |  |

| Simple dual-port mode                  | $\checkmark$                                     |  |  |  |  |

| True dual-port mode                    | $\checkmark$                                     |  |  |  |  |

| Embedded shift register mode (1)       | $\checkmark$                                     |  |  |  |  |

| ROM mode                               | $\checkmark$                                     |  |  |  |  |

| FIFO buffer (1)                        | $\checkmark$                                     |  |  |  |  |

| Simple dual-port mixed width support   | $\checkmark$                                     |  |  |  |  |

| True dual-port mixed width support (2) | $\checkmark$                                     |  |  |  |  |

| Memory initialization file (.mif)      | $\checkmark$                                     |  |  |  |  |

| Mixed-clock mode                       | $\checkmark$                                     |  |  |  |  |

| Power-up condition                     | Outputs cleared                                  |  |  |  |  |

| Register asynchronous clears           | Read address registers and output registers only |  |  |  |  |

| Latch asynchronous clears              | Output latches only                              |  |  |  |  |

| Write or read operation triggering     | Write and read: Rising clock edges               |  |  |  |  |

| Same-port read-during-write            | Outputs set to Old Data or New Data              |  |  |  |  |

| Mixed-port read-during-write           | Outputs set to Old Data or Don't Care            |  |  |  |  |

#### Notes to Table 3-1:

- (1) FIFO buffers and embedded shift registers that require external logic elements (LEs) for implementing control logic.

- (2) Width modes of  $\times$ 32 and  $\times$ 36 are not available.

- For information about the number of M9K memory blocks for Cyclone IV devices, refer to the Cyclone IV Device Family Overview chapter in volume 1 of the Cyclone IV Device Handbook.

### **Control Signals**

The clock-enable control signal controls the clock entering the input and output registers and the entire M9K memory block. This signal disables the clock so that the M9K memory block does not see any clock edges and does not perform any operations.

The rden and wren control signals control the read and write operations for each port of M9K memory blocks. You can disable the rden or wren signals independently to save power whenever the operation is not required.

### **Parity Bit Support**

Parity checking for error detection is possible with the parity bit along with internal logic resources. Cyclone IV devices M9K memory blocks support a parity bit for each storage byte. You can use this bit as either a parity bit or as an additional data bit. No parity function is actually performed on this bit.

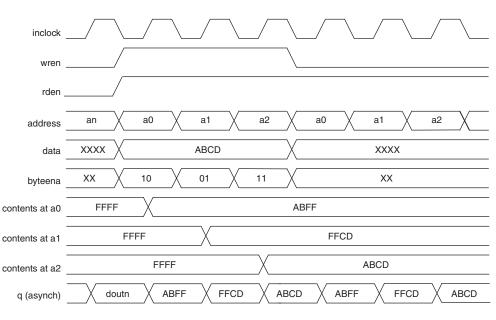

#### **Byte Enable Support**

Cyclone IV devices M9K memory blocks support byte enables that mask the input data so that only specific bytes of data are written. The unwritten bytes retain the previous written value. The wren signals, along with the byte-enable (byteena) signals, control the write operations of the RAM block. The default value of the byteena signals is high (enabled), in which case writing is controlled only by the wren signals. There is no clear port to the byteena registers. M9K blocks support byte enables when the write port has a data width of ×16, ×18, ×32, or ×36 bits.

Byte enables operate in one-hot manner, with the LSB of the byteena signal corresponding to the least significant byte of the data bus. For example, if byteena = 01 and you are using a RAM block in ×18 mode, data[8..0] is enabled and data[17..9] is disabled. Similarly, if byteena = 11, both data[8..0] and data[17..9] are enabled. Byte enables are active high.

Table 3–2 lists the byte selection.

|             | Affected Bytes |            |            |            |  |  |  |

|-------------|----------------|------------|------------|------------|--|--|--|

| byteena[30] | datain ×16     | datain ×18 | datain ×32 | datain ×36 |  |  |  |

| [0] = 1     | [70]           | [80]       | [70]       | [80]       |  |  |  |

| [1] = 1     | [158]          | [179]      | [158]      | [179]      |  |  |  |

| [2] = 1     | —              |            | [2316]     | [2618]     |  |  |  |

| [3] = 1     | _              |            | [3124]     | [3527]     |  |  |  |

Table 3–2.

byteena for Cyclone IV Devices M9K Blocks

(Note 1)

Note to Table 3-2:

(1) Any combination of byte enables is possible.

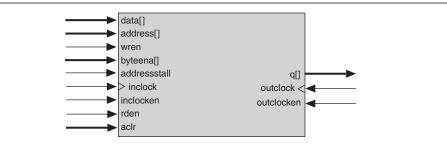

Figure 3–1 shows how the wren and byteena signals control the RAM operations.

Figure 3–1. Cyclone IV Devices byteena Functional Waveform (Note 1)

#### Note to Figure 3-1:

(1) For this functional waveform, New Data mode is selected.

When a byteena bit is deasserted during a write cycle, the old data in the memory appears in the corresponding data-byte output. When a byteena bit is asserted during a write cycle, the corresponding data-byte output depends on the setting chosen in the Quartus® II software. The setting can either be the newly written data or the old data at that location.

### **Packed Mode Support**

Cyclone IV devices M9K memory blocks support packed mode. You can implement two single-port memory blocks in a single block under the following conditions:

- Each of the two independent block sizes is less than or equal to half of the M9K block size. The maximum data width for each independent block is 18 bits wide.

- Each of the single-port memory blocks is configured in single-clock mode. For more information about packed mode support, refer to "Single-Port Mode" on page 3–7 and "Single-Clock Mode" on page 3–15.

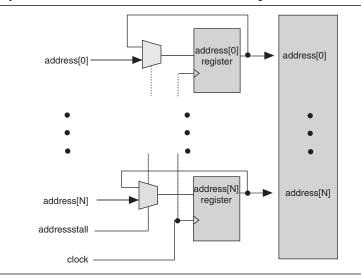

#### Address Clock Enable Support

Cyclone IV devices M9K memory blocks support an active-low address clock enable, which holds the previous address value for as long as the addressstall signal is high (addressstall = '1'). When you configure M9K memory blocks in dual-port mode, each port has its own independent address clock enable.

Figure 3–2 shows an address clock enable block diagram. The address register output feeds back to its input using a multiplexer. The multiplexer output is selected by the address clock enable (addressstall) signal.

Figure 3–2. Cyclone IV Devices Address Clock Enable Block Diagram

The address clock enable is typically used to improve the effectiveness of cache memory applications during a cache-miss. The default value for the address clock enable signals is low.

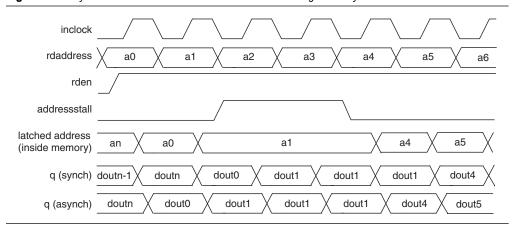

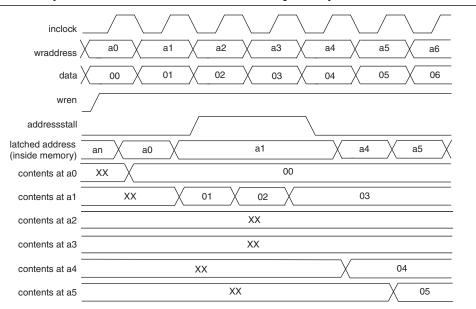

Figure 3–3 and Figure 3–4 show the address clock enable waveform during read and write cycles, respectively.

Figure 3–3. Cyclone IV Devices Address Clock Enable During Read Cycle Waveform

Figure 3–4. Cyclone IV Devices Address Clock Enable During Write Cycle Waveform

#### **Mixed-Width Support**

M9K memory blocks support mixed data widths. When using simple dual-port, true dual-port, or FIFO modes, mixed width support allows you to read and write different data widths to an M9K memory block. For more information about the different widths supported per memory mode, refer to "Memory Modes" on page 3–7.

#### **Asynchronous Clear**

Cyclone IV devices support asynchronous clears for read address registers, output registers, and output latches only. Input registers other than read address registers are not supported. When applied to output registers, the asynchronous clear signal clears the output registers and the effects are immediately seen. If your RAM does not use output registers, you can still clear the RAM outputs using the output latch asynchronous clear feature.

Asserting asynchronous clear to the read address register during a read operation may corrupt the memory content.

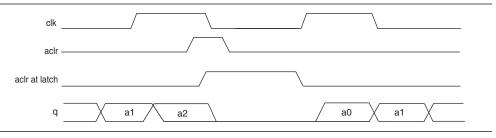

Figure 3–5 shows the functional waveform for the asynchronous clear feature.

Figure 3–5. Output Latch Asynchronous Clear Waveform

You can selectively enable asynchronous clears per logical memory using the Quartus II RAM MegaWizard<sup>™</sup> Plug-In Manager.

**For more information, refer to the** *RAM Megafunction User Guide*.

There are three ways to reset registers in the M9K blocks:

- Power up the device

- Use the aclr signal for output register only

- Assert the device-wide reset signal using the **DEV\_CLRn** option

## **Memory Modes**

Cyclone IV devices M9K memory blocks allow you to implement fully-synchronous SRAM memory in multiple modes of operation. Cyclone IV devices M9K memory blocks do not support asynchronous (unregistered) memory inputs.

M9K memory blocks support the following modes:

- Single-port

- Simple dual-port

- True dual-port

- Shift-register

- ROM

- FIFO

Violating the setup or hold time on the M9K memory block input registers may corrupt memory contents. This applies to both read and write operations.

#### Single-Port Mode

Single-port mode supports non-simultaneous read and write operations from a single address. Figure 3–6 shows the single-port memory configuration for Cyclone IV devices M9K memory blocks.

#### Figure 3-6. Single-Port Memory (Note 1), (2)

#### Notes to Figure 3-6:

- (1) You can implement two single-port memory blocks in a single M9K block.

- (2) For more information, refer to "Packed Mode Support" on page 3-4.

During a write operation, the behavior of the RAM outputs is configurable. If you activate rden during a write operation, the RAM outputs show either the new data being written or the old data at that address. If you perform a write operation with rden deactivated, the RAM outputs retain the values they held during the most recent active rden signal.

To choose the desired behavior, set the **Read-During-Write** option to either **New Data** or **Old Data** in the RAM MegaWizard Plug-In Manager in the Quartus II software. For more information about read-during-write mode, refer to "Read-During-Write Operations" on page 3–15.

The port width configurations for M9K blocks in single-port mode are as follow:

- 8192 × 1

- 4096 × 2

- 2048 × 4

- 1024 × 8

- 1024 × 9

- 512 × 16

- 512 × 18

- 256 × 32

- 256 × 36

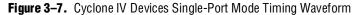

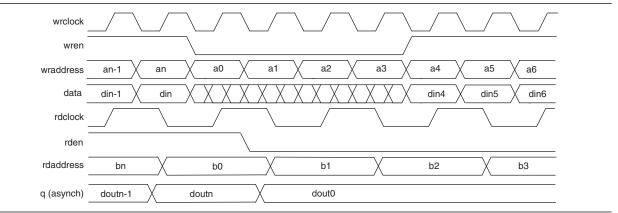

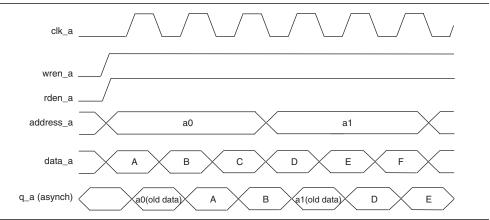

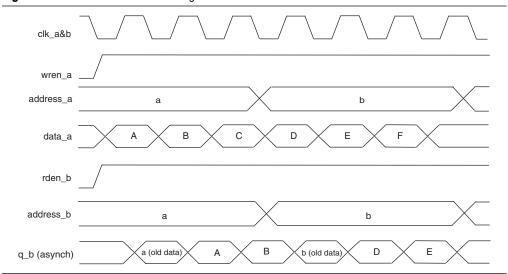

Figure 3–7 shows a timing waveform for read and write operations in single-port mode with unregistered outputs. Registering the outputs of the RAM simply delays the q output by one clock cycle.

### **Simple Dual-Port Mode**

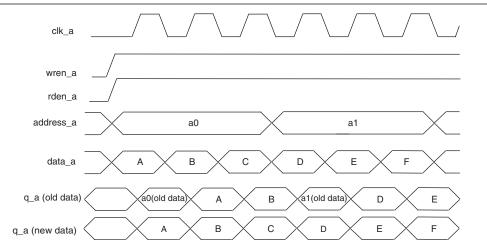

Simple dual-port mode supports simultaneous read and write operations to different locations. Figure 3–8 shows the simple dual-port memory configuration.

#### Note to Figure 3-8:

(1) Simple dual-port RAM supports input or output clock mode in addition to the read or write clock mode shown.

Cyclone IV devices M9K memory blocks support mixed-width configurations, allowing different read and write port widths. Table 3–3 lists mixed-width configurations.

|           | Write Port   |              |              |              |              |              |              |              |              |

|-----------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Read Port | 8192 × 1     | 4096 × 2     | 2048 × 4     | 1024 × 8     | 512 × 16     | 256 × 32     | 1024 × 9     | 512 × 18     | 256 × 36     |

| 8192 × 1  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | —            | —            | —            |

| 4096 × 2  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _            | —            | _            |

| 2048 × 4  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _            | —            |              |

| 1024 × 8  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | —            | —            | _            |

| 512 × 16  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _            | —            | _            |

| 256 × 32  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _            | _            |              |

| 1024 × 9  | _            | _            | —            | _            | _            | _            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| 512 × 18  | —            | —            | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| 256 × 36  | —            | —            | —            | _            | —            | —            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

Table 3-3. Cyclone IV Devices M9K Block Mixed-Width Configurations (Simple Dual-Port Mode)

In simple dual-port mode, M9K memory blocks support separate wren and rden signals. You can save power by keeping the rden signal low (inactive) when not reading. Read-during-write operations to the same address can either output "Don't Care" data at that location or output "Old Data". To choose the desired behavior, set the **Read-During-Write** option to either **Don't Care** or **Old Data** in the RAM MegaWizard Plug-In Manager in the Quartus II software. For more information about this behavior, refer to "Read-During-Write Operations" on page 3–15.

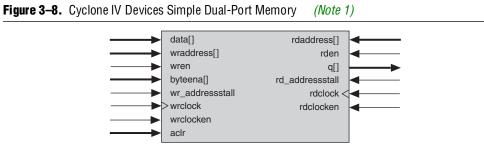

Figure 3–9 shows the timing waveform for read and write operations in simple dual-port mode with unregistered outputs. Registering the outputs of the RAM simply delays the q output by one clock cycle.

### **True Dual-Port Mode**

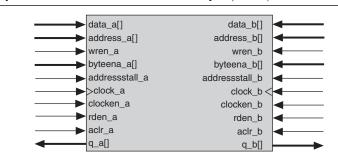

True dual-port mode supports any combination of two-port operations: two reads, two writes, or one read and one write, at two different clock frequencies. Figure 3–10 shows Cyclone IV devices true dual-port memory configuration.

Figure 3–10. Cyclone IV Devices True Dual-Port Memory (Note 1)

#### Note to Figure 3-10:

(1) True dual-port memory supports input or output clock mode in addition to the independent clock mode shown.

The widest bit configuration of the M9K blocks in true dual-port mode is 512 × 16-bit (18-bit with parity).

|           | Write Port   |              |              |              |              |              |              |  |

|-----------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--|

| Read Port | 8192 × 1     | 4096 × 2     | 2048 × 4     | 1024 × 8     | 512 × 16     | 1024 × 9     | 512 × 18     |  |

| 8192 × 1  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | —            | —            |  |

| 4096 × 2  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | —            | _            |  |

| 2048 × 4  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _            |              |  |

| 1024 × 8  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _            | _            |  |

| 512 × 16  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | —            | _            |  |

| 1024 × 9  | _            | _            | —            | _            | _            | $\checkmark$ | $\checkmark$ |  |

| 512 × 18  | —            | —            | —            | _            | _            | $\checkmark$ | $\checkmark$ |  |

Table 3-4 lists the possible M9K block mixed-port width configurations.

In true dual-port mode, M9K memory blocks support separate wren and rden signals. You can save power by keeping the rden signal low (inactive) when not reading. Read-during-write operations to the same address can either output "New Data" at that location or "Old Data". To choose the desired behavior, set the **Read-During-Write** option to either **New Data** or **Old Data** in the RAM MegaWizard Plug-In Manager in the Quartus II software. For more information about this behavior, refer to "Read-During-Write Operations" on page 3–15.

In true dual-port mode, you can access any memory location at any time from either port A or port B. However, when accessing the same memory location from both ports, you must avoid possible write conflicts. When you attempt to write to the same address location from both ports at the same time, a write conflict happens. This results in unknown data being stored to that address location. There is no conflict resolution circuitry built into the Cyclone IV devices M9K memory blocks. You must handle address conflicts external to the RAM block.

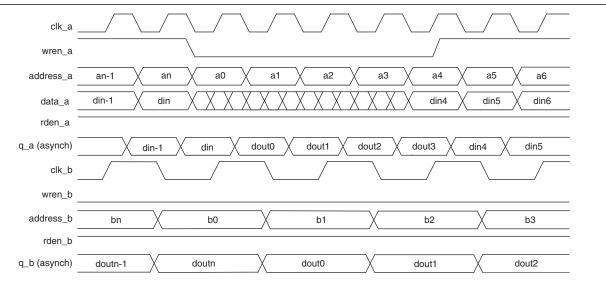

Figure 3–11 shows true dual-port timing waveforms for the write operation at port A and read operation at port B. Registering the outputs of the RAM simply delays the q outputs by one clock cycle.

Table 3-4. Cyclone IV Devices M9K Block Mixed-Width Configurations (True Dual-Port Mode)

Figure 3–11. Cyclone IV Devices True Dual-Port Timing Waveform

### **Shift Register Mode**

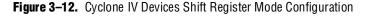

Cyclone IV devices M9K memory blocks can implement shift registers for digital signal processing (DSP) applications, such as finite impulse response (FIR) filters, pseudo-random number generators, multi-channel filtering, and auto-correlation and cross-correlation functions. These and other DSP applications require local data storage, traditionally implemented with standard flipflops that quickly exhaust many logic cells for large shift registers. A more efficient alternative is to use embedded memory as a shift register block, which saves logic cell and routing resources.

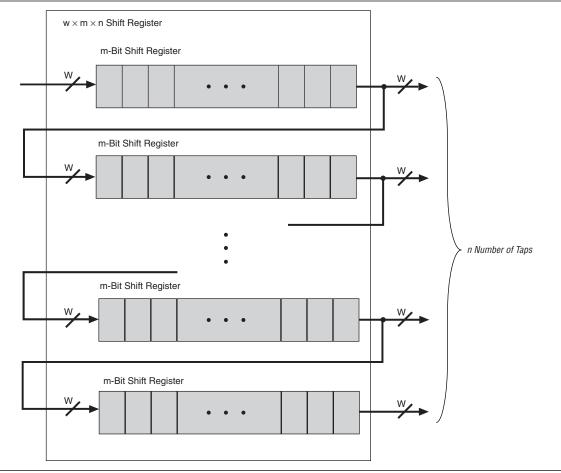

The size of a  $(w \times m \times n)$  shift register is determined by the input data width (w), the length of the taps (m), and the number of taps (n), and must be less than or equal to the maximum number of memory bits, which is 9,216 bits. In addition, the size of  $(w \times n)$  must be less than or equal to the maximum width of the block, which is 36 bits. If you need a larger shift register, you can cascade the M9K memory blocks.

Figure 3–12 shows the Cyclone IV devices M9K memory block in shift register mode.

### **ROM Mode**

Cyclone IV devices M9K memory blocks support ROM mode. A **.mif** initializes the ROM contents of these blocks. The address lines of the ROM are registered. The outputs can be registered or unregistered. The ROM read operation is identical to the read operation in the single-port RAM configuration.

### **FIFO Buffer Mode**

Cyclone IV devices M9K memory blocks support single-clock or dual-clock FIFO buffers. Dual clock FIFO buffers are useful when transferring data from one clock domain to another clock domain. Cyclone IV devices M9K memory blocks do not support simultaneous read and write from an empty FIFO buffer.

For more information about FIFO buffers, refer to the *Single- and Dual-Clock FIFO Megafunction User Guide*.

# **Clocking Modes**

Cyclone IV devices M9K memory blocks support the following clocking modes:

- Independent

- Input or output

- Read or write

- Single-clock

When using read or write clock mode, if you perform a simultaneous read or write to the same address location, the output read data is unknown. If you require the output data to be a known value, use either single-clock mode or I/O clock mode and choose the appropriate read-during-write behavior in the MegaWizard Plug-In Manager.

Violating the setup or hold time on the memory block input registers might corrupt the memory contents. This applies to both read and write operations.

Asynchronous clears are available on read address registers, output registers, and output latches only.

Table 3–5 lists the clocking mode versus memory mode support matrix.

| Clocking Mode   | True Dual-Port<br>Mode | Simple<br>Dual-Port<br>Mode | Single-Port<br>Mode   | ROM Mode     | FIFO Mode    |

|-----------------|------------------------|-----------------------------|-----------------------|--------------|--------------|

| Independent     | $\checkmark$           | —                           | —                     | ~            | —            |

| Input or output | $\checkmark$           | $\checkmark$                | <ul> <li>✓</li> </ul> | ~            | —            |

| Read or write   |                        | $\checkmark$                | —                     | —            | ~            |

| Single-clock    | ~                      | $\checkmark$                | <ul> <li></li> </ul>  | $\checkmark$ | $\checkmark$ |

Table 3-5. Cyclone IV Devices Memory Clock Modes

## **Independent Clock Mode**

Cyclone IV devices M9K memory blocks can implement independent clock mode for true dual-port memories. In this mode, a separate clock is available for each port (port A and port B). clock A controls all registers on the port A side, while clock B controls all registers on the port B side. Each port also supports independent clock enables for port A and B registers.

## **Input or Output Clock Mode**

Cyclone IV devices M9K memory blocks can implement input or output clock mode for FIFO, single-port, true, and simple dual-port memories. In this mode, an input clock controls all input registers to the memory block including data, address, byteena, wren, and rden registers. An output clock controls the data-output registers. Each memory block port also supports independent clock enables for input and output registers.

### **Read or Write Clock Mode**

Cyclone IV devices M9K memory blocks can implement read or write clock mode for FIFO and simple dual-port memories. In this mode, a write clock controls the data inputs, write address, and wren registers. Similarly, a read clock controls the data outputs, read address, and rden registers. M9K memory blocks support independent clock enables for both the read and write clocks.

When using read or write mode, if you perform a simultaneous read or write to the same address location, the output read data is unknown. If you require the output data to be a known value, use either single-clock mode, input clock mode, or output clock mode and choose the appropriate read-during-write behavior in the MegaWizard Plug-In Manager.

#### **Single-Clock Mode**

Cyclone IV devices M9K memory blocks can implement single-clock mode for FIFO, ROM, true dual-port, simple dual-port, and single-port memories. In this mode, you can control all registers of the M9K memory block with a single clock together with clock enable.

## **Design Considerations**

This section describes designing with M9K memory blocks.

#### **Read-During-Write Operations**

"Same-Port Read-During-Write Mode" on page 3–16 and "Mixed-Port Read-During-Write Mode" on page 3–17 describe the functionality of the various RAM configurations when reading from an address during a write operation at that same address.

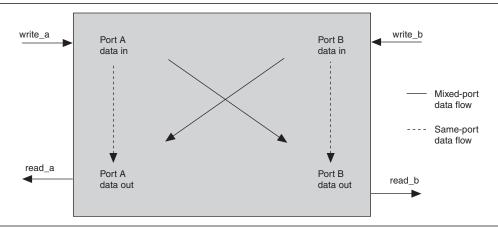

There are two read-during-write data flows: same-port and mixed-port. Figure 3–13 shows the difference between these flows.

Figure 3–13. Cyclone IV Devices Read-During-Write Data Flow

#### Same-Port Read-During-Write Mode

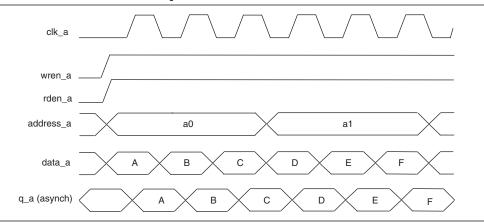

This mode applies to a single-port RAM or the same port of a true dual-port RAM. In the same port read-during-write mode, there are two output choices: **New Data** mode (or flow-through) and **Old Data** mode. In **New Data** mode, new data is available on the rising edge of the same clock cycle on which it was written. In **Old Data** mode, the RAM outputs reflect the old data at that address before the write operation proceeds.

When using **New Data** mode together with byteena, you can control the output of the RAM. When byteena is high, the data written into the memory passes to the output (flow-through). When byteena is low, the masked-off data is not written into the memory and the old data in the memory appears on the outputs. Therefore, the output can be a combination of new and old data determined by byteena.

Figure 3–14 and Figure 3–15 show sample functional waveforms of same port read-during-write behavior with both **New Data** and **Old Data** modes, respectively.

Figure 3-14. Same Port Read-During Write: New Data Mode

#### **Mixed-Port Read-During-Write Mode**

This mode applies to a RAM in simple or true dual-port mode, which has one port reading and the other port writing to the same address location with the same clock.

In this mode, you also have two output choices: **Old Data** mode or **Don't Care** mode. In **Old Data** mode, a read-during-write operation to different ports causes the RAM outputs to reflect the old data at that address location. In **Don't Care** mode, the same operation results in a "Don't Care" or unknown value on the RAM outputs.

For more information about how to implement the desired behavior, refer to the *RAM Megafunction User Guide*.

Figure 3–16 shows a sample functional waveform of mixed port read-during-write behavior for **Old Data** mode. In **Don't Care** mode, the old data is replaced with "Don't Care".

Figure 3–16. Mixed Port Read-During-Write: Old Data Mode

## **Conflict Resolution**

When you are using M9K memory blocks in true dual-port mode, it is possible to attempt two write operations to the same memory location (address). Because there is no conflict resolution circuitry built into M9K memory blocks, this results in unknown data being written to that location. Therefore, you must implement conflict-resolution logic external to the M9K memory block.

For mixed-port read-during-write operation with dual clocks, the relationship between the clocks determines the output behavior of the memory. If you use the same clock for the two clocks, the output is the old data from the address location. However, if you use different clocks, the output is unknown during the mixed-port read-during-write operation. This unknown value may be the old or new data at the address location, depending on whether the read happens before or after the write.

# **Power-Up Conditions and Memory Initialization**

The M9K memory block outputs of Cyclone IV devices power up to zero (cleared) regardless of whether the output registers are used or bypassed. All M9K memory blocks support initialization using a **.mif**. You can create **.mif**s in the Quartus II software and specify their use using the RAM MegaWizard Plug-In Manager when instantiating memory in your design. Even if memory is pre-initialized (for example, using a **.mif**), it still powers up with its outputs cleared. Only the subsequent read after power up outputs the pre-initialized values.

For more information about **.mifs**, refer to the *RAM Megafunction User Guide* and the *Quartus II Handbook*.

## **Power Management**

The M9K memory block clock enables of Cyclone IV devices allow you to control clocking of each M9K memory block to reduce AC power consumption. Use the rden signal to ensure that read operations only occur when necessary. If your design does not require read-during-write, reduce power consumption by deasserting the rden signal during write operations or any period when there are no memory operations. The Quartus II software automatically powers down any unused M9K memory blocks to save static power.

# **Chapter Revision History**

Table 3–6 shows the revision history for this chapter.

**Table 3–6.** Chapter Revision History

| Date          | Version | Changes Made     |

|---------------|---------|------------------|

| November 2009 | 1.0     | Initial release. |

# 4. Embedded Multipliers in Cyclone IV Devices

CYIV-51004-1.0

Cyclone® IV devices include a combination of on-chip resources and external interfaces that help to increase performance, reduce system cost, and lower the power consumption of digital signal processing (DSP) systems. Cyclone IV devices, either alone or as DSP device co-processors, are used to improve price-to-performance ratios of DSP systems. Particular focus is placed on optimizing Cyclone IV devices for applications that benefit from an abundance of parallel processing resources, which include video and image processing, intermediate frequency (IF) modems used in wireless communications systems, and multi-channel communications and video systems.

References to Cyclone IV devices in this chapter refer only to Cyclone IV GX devices. Information about Cyclone IV E devices will be included in a future revision of this chapter.

This chapter contains the following sections:

- "Embedded Multiplier Block Overview" on page 4–1

- "Architecture" on page 4–2

- "Operational Modes" on page 4–4

# **Embedded Multiplier Block Overview**

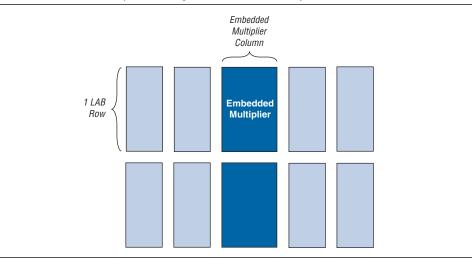

Figure 4–1 shows one of the embedded multiplier columns with the surrounding logic array blocks (LABs). The embedded multiplier is configured as either one  $18 \times 18$  multiplier or two  $9 \times 9$  multipliers. For multiplications greater than  $18 \times 18$ , the Quartus® II software cascades multiple embedded multiplier blocks together. There are no restrictions on the data width of the multiplier, but the greater the data width, the slower the multiplication process.

Figure 4-1. Embedded Multipliers Arranged in Columns with Adjacent LABs

Table 4–1 shows the number of embedded multipliers and the multiplier modes that can be implemented in each Cyclone IV device.

| Device Family | Device    | Embedded<br>Multipliers | 9 × 9<br>Multipliers (1) | 18 × 18<br>Multipliers (1) | Software<br>Multipliers (2) | Total<br>Multipliers (3) |

|---------------|-----------|-------------------------|--------------------------|----------------------------|-----------------------------|--------------------------|

|               | EP4CGX15  | 0                       | 0                        | 0                          | 60                          | 60                       |

|               | EP4CGX22  | 40                      | 80                       | 40                         | 84                          | 124                      |

|               | EP4CGX30  | 80                      | 160                      | 80                         | 120                         | 200                      |

| Cyclone IV    | EP4CGX50  | 140                     | 280                      | 140                        | 278                         | 418                      |

|               | EP4CGX75  | 198                     | 396                      | 198                        | 462                         | 660                      |

|               | EP4CGX110 | 280                     | 560                      | 280                        | 610                         | 890                      |

|               | EP4CGX150 | 360                     | 720                      | 360                        | 720                         | 1080                     |

Table 4-1. Number of Embedded Multipliers in Cyclone IV Devices

#### Notes to Table 4-1:

(1) These columns show the number of  $9 \times 9$  or  $18 \times 18$  multipliers for each device.

(2) Soft multipliers are implemented in sum of multiplication mode. M9K memory blocks are configured with 18-bit data widths to support 16-bit coefficients. The sum of the coefficients requires 18 bits of resolution to account for overflow.

(3) The total number of multipliers may vary, depending on the multiplier mode used.

In addition to the embedded multipliers in Cyclone IV devices, you can implement soft multipliers by using the M9K memory blocks as look-up tables (LUTs). The LUTs contain partial results from the multiplication of input data with coefficients that implement variable depth and width high-performance soft multipliers for low-cost, high-volume DSP applications. The availability of soft multipliers increases the number of available multipliers in the device.

For more information about M9K memory blocks, refer to the *Memory Blocks in Cyclone IV Devices* chapter in volume 1 of the *Cyclone IV Device Handbook*.

For more information about soft multipliers, refer to AN 306: Implementing Multipliers in FPGA Devices.

# Architecture

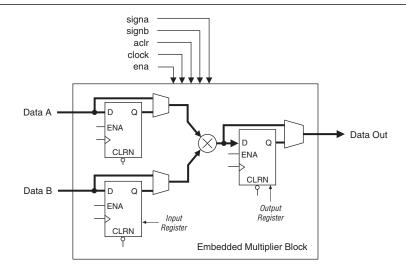

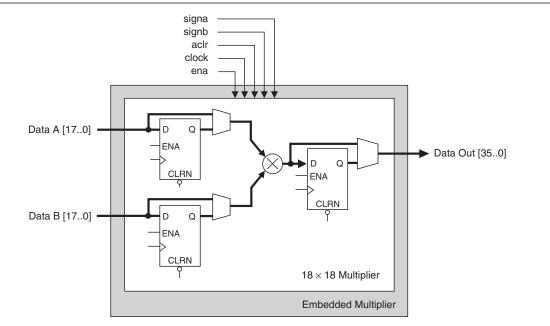

Each embedded multiplier consists of the following elements:

- Multiplier stage

- Input and output registers

- Input and output interfaces

Figure 4–2 shows the multiplier block architecture.

### **Input Registers**

You can send each multiplier input signal into an input register or directly into the multiplier in 9- or 18-bit sections, depending on the operational mode of the multiplier. Each multiplier input signal can be sent through a register independently of other input signals. For example, you can send the multiplier Data A signal through a register and send the Data B signal directly to the multiplier.

The following control signals are available for each input register in the embedded multiplier:

- clock

- clock enable

- asynchronous clear

All input and output registers in a single embedded multiplier are fed by the same clock, clock enable, and asynchronous clear signals.

### **Multiplier Stage**

The multiplier stage of an embedded multiplier block supports  $9 \times 9$  or  $18 \times 18$  multipliers as well as other multipliers between these configurations. Depending on the data width or operational mode of the multiplier, a single embedded multiplier can perform one or two multiplications in parallel. For multiplier information, refer to "Operational Modes" on page 4–4.

Each multiplier operand is a unique signed or unsigned number. Two signals, signa and signb, control an input of a multiplier and determine if the value is signed or unsigned. If the signa signal is high, the Data A operand is a signed number. If the signa signal is low, the Data A operand is an unsigned number.

Table 4–2 shows the sign of the multiplication results for the various operand sign representations. The results of the multiplication are signed if any one of the operands is a signed value.

| Dat         | ta A        | Dat         | ta B        |          |

|-------------|-------------|-------------|-------------|----------|

| signa Value | Logic Level | signb Value | Logic Level | Result   |

| Unsigned    | Low         | Unsigned    | Low         | Unsigned |

| Unsigned    | Low         | Signed      | High        | Signed   |

| Signed      | High        | Unsigned    | Low         | Signed   |

| Signed      | High        | Signed      | High        | Signed   |

| Table 4-2. | Multiplier | Sian  | Representation  |

|------------|------------|-------|-----------------|

|            | manuphor   | o ign | rioprocontation |

Each embedded multiplier block has only one signa and one signb signal to control the sign representation of the input data to the block. If the embedded multiplier block has two 9 × 9 multipliers, the Data A input of both multipliers share the same signa signal, and the Data B input of both multipliers share the same signb signal. You can dynamically change the signa and signb signals to modify the sign representation of the input operands at run time. You can send the signa and signb signals through a dedicated input register. The multiplier offers full precision, regardless of the sign representation.

P

When the signa and signb signals are unused, the Quartus II software sets the multiplier to perform unsigned multiplication by default.

### **Output Registers**

You can register the embedded multiplier output using output registers in either 18- or 36-bit sections, depending on the operational mode of the multiplier. The following control signals are available for each output register in the embedded multiplier:

- clock

- clock enable

- asynchronous clear

All input and output registers in a single embedded multiplier are fed by the same clock, clock enable, and asynchronous clear signals.

# **Operational Modes**

You can use an embedded multiplier block in one of two operational modes, depending on the application needs:

- One 18-bit × 18-bit multiplier

- Up to two 9-bit × 9-bit independent multipliers

You can also use embedded multipliers of Cyclone IV devices to implement multiplier adder and multiplier accumulator functions, in which the multiplier portion of the function is implemented using embedded multipliers, and the adder or accumulator function is implemented in logic elements (LEs).

## **18-Bit Multipliers**

You can configure each embedded multiplier to support a single  $18 \times 18$  multiplier for input widths of 10 to 18 bits.

Figure 4–3 shows the embedded multiplier configured to support an 18-bit multiplier.

All 18-bit multiplier inputs and results are independently sent through registers. The multiplier inputs can accept signed integers, unsigned integers, or a combination of both. Also, you can dynamically change the signa and signb signals and send these signals through dedicated input registers.

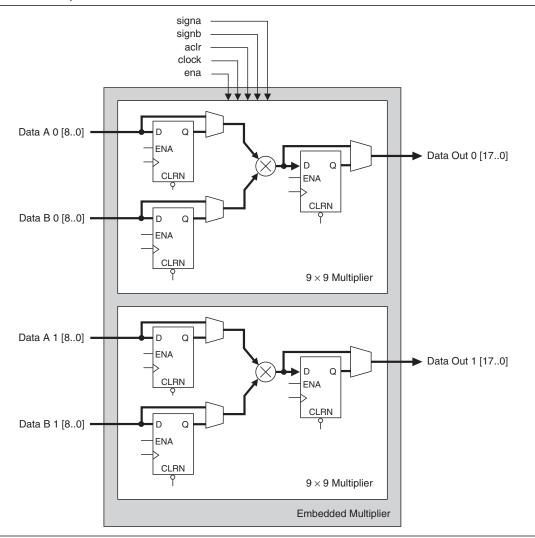

## 9-Bit Multipliers

You can configure each embedded multiplier to support two  $9 \times 9$  independent multipliers for input widths of up to 9 bits.

Figure 4–4 shows the embedded multiplier configured to support two 9-bit multipliers.

#### Figure 4-4. 9-Bit Multiplier Mode

All 9-bit multiplier inputs and results are independently sent through registers. The multiplier inputs can accept signed integers, unsigned integers, or a combination of both. Two 9 × 9 multipliers in the same embedded multiplier block share the same signa and signb signal. Therefore, all the Data A inputs feeding the same embedded multiplier must have the same sign representation. Similarly, all the Data B inputs feeding the same embedded multiplier must have the same sign representation.

# **Chapter Revision History**

Table 4–3 shows the revision history for this chapter.

| Table 4-3. | Chapter | Revision | History |

|------------|---------|----------|---------|

|------------|---------|----------|---------|

| Date          | Version | Changes Made     |

|---------------|---------|------------------|

| November 2009 | 1.0     | Initial release. |

# 5. Clock Networks and PLLs in Cyclone IV Devices

#### CYIV-51005-1.0

This chapter describes the hierarchical clock networks and phase-locked loops (PLLs) with advanced features in Cyclone<sup>®</sup> IV devices.

References to Cyclone IV devices in this chapter refer only to Cyclone IV GX devices. Information about Cyclone IV E devices will be included in a future revision of this chapter.

This chapter includes the following sections:

- "Clock Networks" on page 5–1

- "PLLs in Cyclone IV Devices" on page 5–13

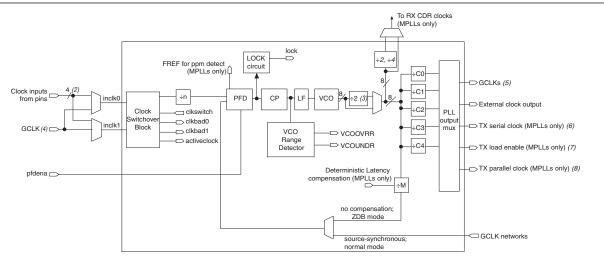

- "Cyclone IV PLL Hardware Overview" on page 5–15

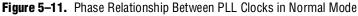

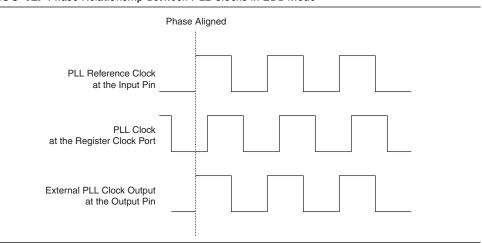

- "Clock Feedback Modes" on page 5–17

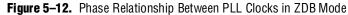

- "Hardware Features" on page 5–21

- "Programmable Bandwidth" on page 5–27

- "Phase Shift Implementation" on page 5–27

- "PLL Cascading" on page 5–29

- "PLL Reconfiguration" on page 5–29

- "Spread-Spectrum Clocking" on page 5–36

- "PLL Specifications" on page 5–36

# **Clock Networks**

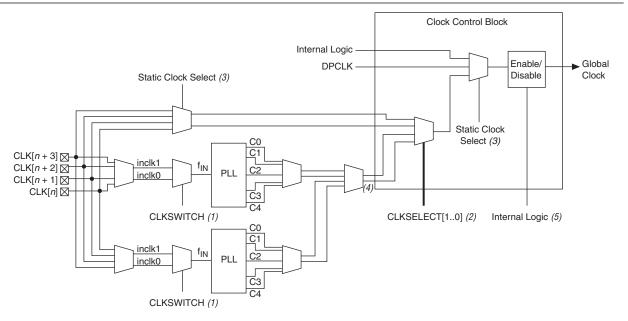

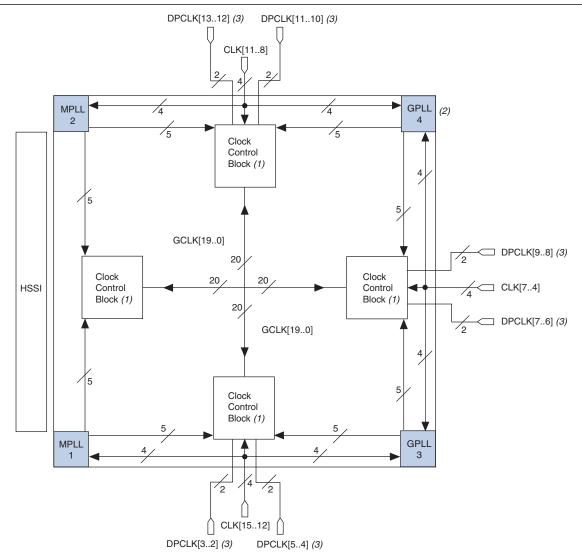

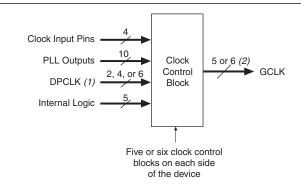

Cyclone IV devices provide up to 12 dedicated clock pins (CLK [15..4]) that can drive the global clocks (GCLKs). Cyclone IV devices support four dedicated clock pins on each side of the device except the left side. These clock pins can drive up to 30 GCLKs.

For more information about the number of GCLK networks in each device density, refer to the Cyclone IV FPGA Device Family Overview chapter in volume 1.

### **GCLK Network**

GCLKs drive throughout the entire device, feeding all device quadrants. All resources in the device (I/O elements, logic array blocks (LABs), dedicated multiplier blocks, and M9K memory blocks) can use GCLKs as clock sources. Use these clock network resources for control signals, such as clock enables and clears fed by an external pin. Internal logic can also drive GCLKs for internally generated GCLKs and asynchronous clears, clock enables, or other control signals with high fan-out. Table 5–1 and Table 5–2 on page 5–4 list the connectivity of the clock sources to the GCLK networks.

| GCLK Network Clock            |              |              |              |              |              |              |              |              | GC           | LK N         | etwo         | rks          |              |              |              |              |              |                      |              |              |

|-------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|----------------------|--------------|--------------|

| Sources                       | 0            | 1            | 2            | 3            | 4            | 5            | 6            | 7            | 8            | 9            | 10           | 11           | 12           | 13           | 14           | 15           | 16           | 17                   | 18           | 19           |

| CLK4/DIFFCLK_2n               | —            | —            | —            | —            | —            | $\checkmark$ | —            | $\checkmark$ | —            | $\checkmark$ | —            | —            | —            | —            | —            | —            | —            | —                    | —            | —            |

| CLK5/DIFFCLK_2p               | —            | _            | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ | —            | —            | -            | —            | —            | —            | —            | —            | —            | —                    | —            | —            |

| CLK6/DIFFCLK_3n               | —            | —            | —            | —            | —            | —            | $\checkmark$ | —            | $\checkmark$ | $\checkmark$ | —            | —            | —            | —            | —            | —            | —            | —                    | —            | _            |

| CLK7/DIFFCLK_3p               | —            | _            | —            | —            | —            | $\checkmark$ | —            | —            | ~            | —            | —            | —            | —            | —            | —            | —            | —            | —                    | —            | _            |

| CLK8/DIFFCLK_5n               | —            | _            | —            |              | —            | —            | —            |              | _            | —            | $\checkmark$ | —            | $\checkmark$ | _            | ~            |              | —            | —                    | —            | —            |

| CLK9/DIFFCLK_5p               | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ | —            | —            | —            | —            | —                    | —            | —            |

| CLK10/DIFFCLK_4n<br>/REFCLK1n | _            | _            | —            |              | —            |              |              |              | _            | _            | -            | ~            | _            | ~            | ~            |              |              |                      | _            |              |

| CLK11/DIFFCLK_4p<br>/REFCLK1p | —            | _            | —            | —            | _            | —            | _            | —            | _            | —            | ~            | _            | —            | ~            | _            | —            | —            | _                    | _            |              |

| CLK12/DIFFCLK_7p<br>/REFCLK0p | -            |              | —            | _            | _            | _            | _            | _            | _            | -            | —            | _            | -            | _            | _            | ~            | _            | ~                    | —            | ~            |

| CLK13/DIFFCLK_7n<br>/REFCLK0n | -            | _            | —            | —            | —            | —            | _            | —            | _            | -            | —            | _            | —            | _            | _            | —            | ~            | ~                    | —            |              |

| CLK14/DIFFCLK_6p              | —            | _            | —            | —            | —            | —            | —            | —            | _            | —            | —            | —            | —            | —            | —            | —            | $\checkmark$ | —                    | $\checkmark$ | $\checkmark$ |

| CLK15/DIFFCLK_6n              | —            | _            | —            |              | —            | —            | —            |              | —            | —            | —            | —            | —            | —            | —            | $\checkmark$ | —            | —                    | $\checkmark$ | —            |

| MPLL1_C0                      | $\checkmark$ | _            | —            | $\checkmark$ | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | $\checkmark$ | —            | —                    | $\checkmark$ | —            |

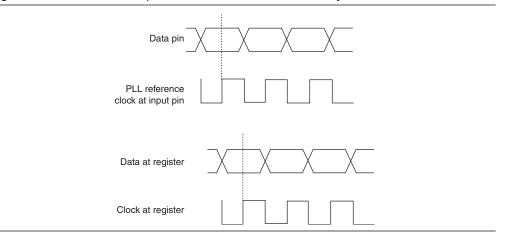

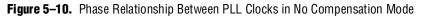

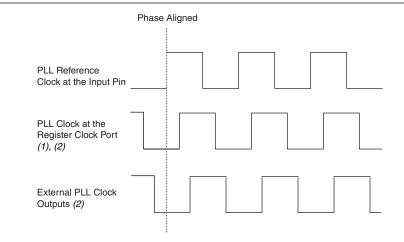

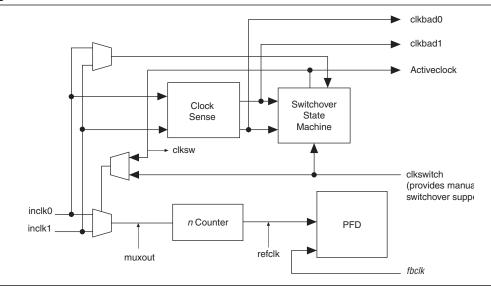

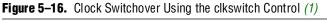

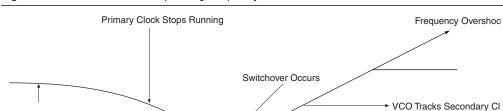

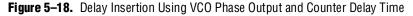

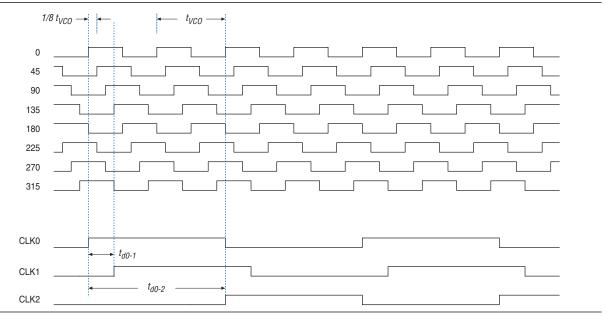

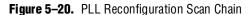

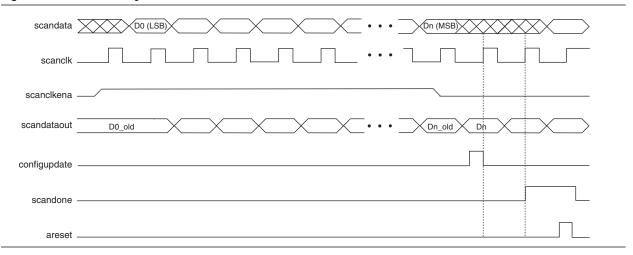

| MPLL1_C1                      | —            | >            | —            | —            | $\checkmark$ | —            | —            | —            | _            | —            | —            | —            | —            | —            | —            | —            | $\checkmark$ | —                    | —            | $\checkmark$ |